## **EEM16** Final

MARK GUEVARA

TOTAL POINTS

## 107.5 / 125

QUESTION 1 Problem #1 30 pts

1.1 (a), (b) 6 / 6

✓ - 0 pts a is correct

$\checkmark$  - **0 pts** b is correct

1.2 (C) - (i) 18.5 / 24

- $\checkmark$  0 pts c correct

- ✓ 0 pts d correct

- $\checkmark$  0.5 pts e 3 product terms

- ✓ 0.5 pts f columns or rows

- ✓ 2 pts g map wrong

- $\checkmark$  2 pts h incorrect

- ✓ 0.5 pts i 12 states

#### QUESTION 2

2 Problem #2 14 / 15

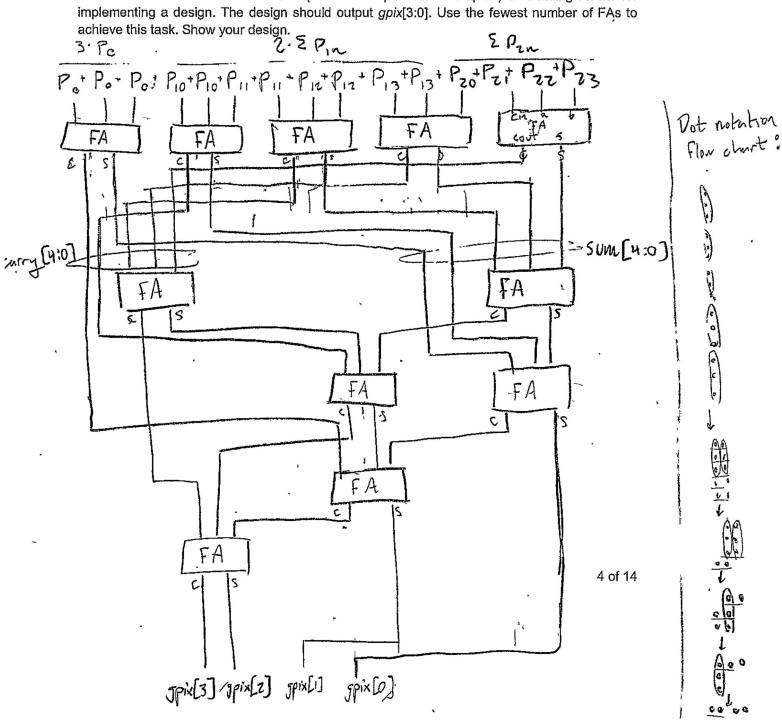

$\checkmark$  - 1 pts Not fewest number of FAs, but correct

## QUESTION 3

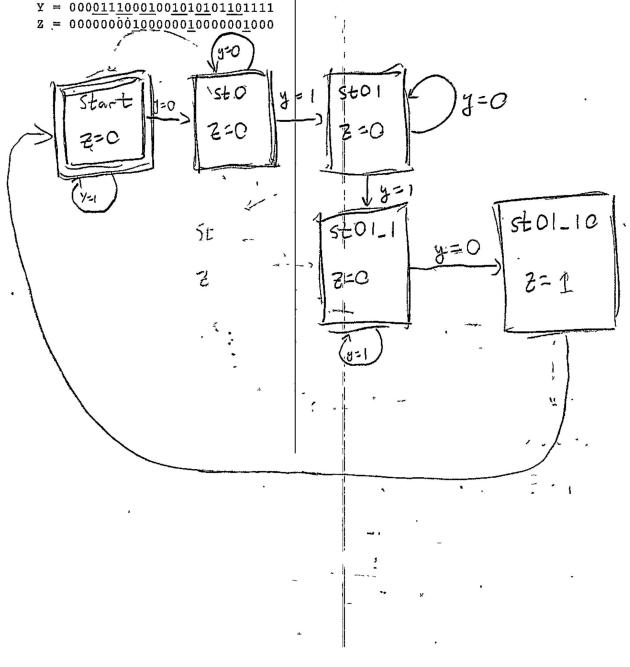

3 Problem #3 13 / 15

$\checkmark$  - 2 pts missing one thing or has an extra state

QUESTION 4

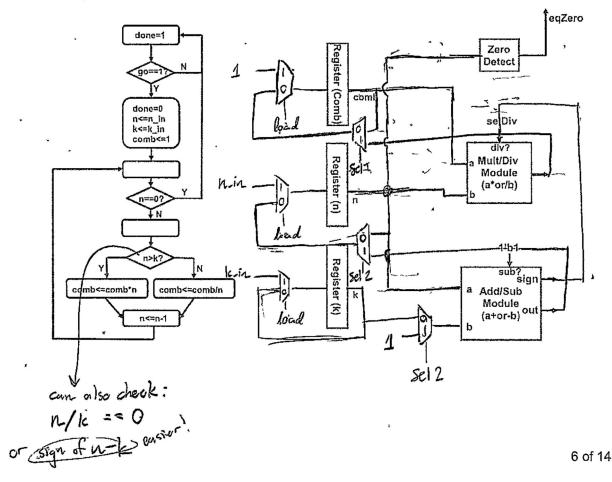

4 Problem #4 20 / 20

## ✓ - 0 pts Correct

#### QUESTION 5

Problem #5 18 pts

5.1 (a)-(c) 7 / 11

- $\checkmark$  2 pts (a) incorrect tccl (14)

- $\checkmark$  2 pts (a) incorrect tdcl (43)

5.2 (d)-(f) 7 / 7

✓ - 0 pts Correct

## QUESTION 6

6 Problem #6 9 / 12

- $\checkmark$  1 pts (a) partial correct

- ✓ 0.5 pts (b)missing reset

- √ 0.5 pts (b) missing st[2:0]

- ✓ 0.5 pts (b)missing in[0]

- $\checkmark$  0.5 pts (b) missing go

## QUESTION 7

- 7 Problem #7 13 / 15

- $\checkmark$  1 pts (e)incorrect setup

- ✓ 1 pts (e)incorrect hold

Prof. C.K. Yang

UCLA | EEM16/CSM51A | Spring 2018

# Final Exam

Name (Last, First): Guevara, Mark Student Id #: 704962920

#### Do not start working until instructed to do so.

- You must answer in the <u>space provided</u> for answers after every question. We will ignore answers written anywhere else in the booklet. <u>All pages in this booklet must be</u> <u>accounted</u> for otherwise it will not be graded.

- 2. You are permitted 2 page of notes 8.5x11 (front and back).

- 3. You may not use any electronic device.

Following table to be filled by course staff only

|            | ال الد موجد منابيتهم موجوا مراحد مراحد مراحد مراجد |

|------------|----------------------------------------------------|

|            | Maximup<br>Score                                   |

| Question 1 | 30                                                 |

| Question 2 | 15 ,                                               |

| Question 3 | 15                                                 |

| Question 4 | 20 -                                               |

| Question 5 | 18                                                 |

| Question 6 | 12                                                 |

| Question 7 | 15 '                                               |

| TOTAL      | 125                                                |

'1 of 14

## Question #1 State Machine to Logic (30)

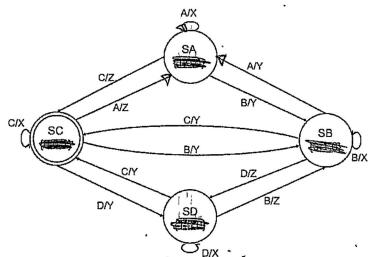

A Mealy FSM state diagram is shown below. This is a decoder for a 3-level to 4-level encoding. A 4-level signal is communicated between two endpoints (A, B, C, and D). This signal is the input to the FSM. Transitions between the levels map to 3 symbols (X, Y, and Z); these symbols are the outputs. Note that some transitions are eliminated to enhance the quality of the communication.

(a) (2) Explain the difference between a Mealy and a Moore FSM.

A Moore machine's outputs depend only on the current state while G Mealy machine's cutputs are a function of the inputs and the current state.

| state | in | out | nx_state |

|-------|----|-----|----------|

| SA    | A  | X   | 5A       |

| · SB  | B  | ×   | SB       |

| 512   | В  | Z   | sB       |

| SC .  | С  | Х   | SC       |

| SD .  | Ç  | Y   | - SC     |

| SC    | A  | モ   | , SA .   |

| SB    | D  | Z   | 5D       |

(b) (4) Fill in the blanks in this partial state transition table.

2 of 14

Â

Prof. C.K. Yang

ι

Assume for the following parts that inputs, outputs and states are all one-hot encoded,

(c) (3) How many bits are needed for the input, output, and states?

A

ř

#### UCLA | EEM16/CSM51A | Spring 2018 Question #2 Logic Design (15)

A field of black ("0") and white ("1") pixels can be "blurred" into gray values by taking a weightedaverage that includes neighboring pixels as shown in the figure. Each converted gray-valued pixel, gpix, is a 4-bit value and is computed from 9 binary inputs, pxy, based on the equation  $gpix_0[3:0] = 3 \cdot p_0 + 2 \cdot \sum p_{1n} + \sum p_{2n}.$

| p <sub>21</sub>        | <i>p</i> <sub>11</sub> | <i>p</i> <sub>20</sub> |

|------------------------|------------------------|------------------------|

| <i>p</i> <sub>12</sub> | p <sub>0</sub>         | <i>p</i> <sub>10</sub> |

| p <sub>22</sub>        | <i>p</i> <sub>13</sub> | ,<br>p <sub>23</sub>   |

You have available 1-bit Full Adders (FA with 3-inputs and 2-outputs) as building blocks for implementing a design. The design should output gpix[3:0]. Use the fewest number of FAs to

Prof. C.K. Yang

## UCLA | EEM16/CSM51A | Spring 2018 Question #3 FSM State Diagram (15)

The input to an FSM, Y, is a string of 1's and 0's. Design a **Moore** FSM that detects when a "01" sequence is followed a "10" sequence. The FSM is reset/initialized to a state for which prior inputs are all 0's. An example of the input and output is shown below and key transitions are underlined. Note that "010" does not constitute a "01" followed by a "10". The output, *Z*, asserts for only 1 cycle when the sequence is detected. As a design constraint, use the fewest number of states.

#### Prof. C.K. Yang

#### UCLA | EEM16/CSM51A | Spring 2018 Question #4 System Partitioning (20)

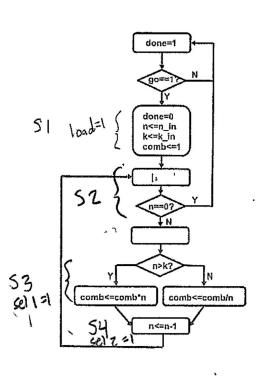

The following algorithm calculates the combinatorics function C(n,k)=n!/(n-k)!k! (commonly referred to as n-choose-k or nCk).

```

n = n_in;

k = k_in;

comb = 1;

while (n > 0) {

if (n>k)

comb = comb*n;

else

comb = comb/n;

n---

}

done = 1

```

The flow diagram is already designed as shown below. A signal, *go*, is an input to the controller that triggers this algorithm. Output, *done*, is asserted by the controller when the algorithm completes and is waiting for the *go* signal. The previous computation is held in the register, *comb*. You are to complete the controller and datapath design.

(a) (10) The datapath blocks available to you are also shown below (a combined multiply/divide module, an add/subtract module, and a zero detect module). You may also use as many 2:1 MUX as you choose (Note that you can only use 2:1 MUX so the select signals for each MUX is a single-bit signal from the controller). You can ignore the bit-width of any of the signals. Show the necessary connections within the datapath and any signals that need to pass as inputs to/from the controller.

1

Prof. C.K. Yang

(b) (10) Design a Moore FSM for the controller. Indicate the desired control signals from controller to the datapath on the FSM state diagram.

Start

$$J_{lood} = 0$$

$sel 1 = 0$

$sel 2 = 0$

$g_{0}$

$g_{0}$

r T

Prof. C.K. Yang

#### Question #5 Timing and Pipelining (18)

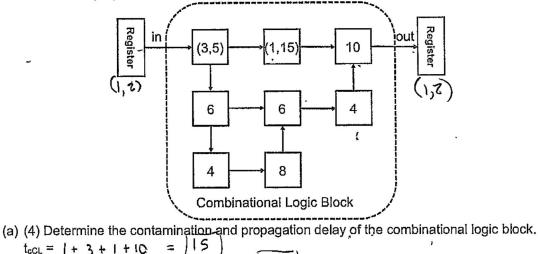

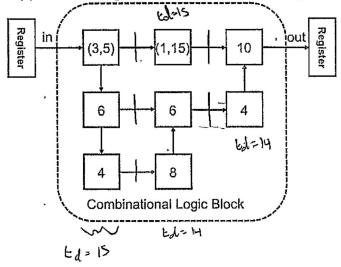

The following combinational logic block can be broken down into modules. Each module have their delay as shown. For each module, the propagation and contamination delay are the same  $(t_c = t_d)$  with the except of two blocks where the  $(t_c, t_d)$  is shown in the block. The registers comprise of DFF with the properties  $t_s = 3$ ,  $t_H=1$ ,  $t_{cQ} = (1,2)$ .

- $t_{\text{CCL}} = 1 + 3 + 1 + 10 = [15]$  $t_{\text{dCL}} = 2 + 5 + 6 + 4 + 5 + 6 + 4 + 10 = [45]$

- (b) (3) What is the minimum cycle time of the combinational logic block?

- $\min(T_{\text{cycle}}) = t_{dCQ} + t_{dMax} + t_{S}$  = 4S + 3 = [48]

- (c) (4) We can minimize the cycle time by inserting registers. Show on the diagram below where to insert the register(s). Indicate a register with a line. Use as few registers as possible.

8 of 14

, I

5

7

Prof. C.K. Yang

(d) (2) Based on the answer in (c) determine the new minimum cycle time.

$$\min(T_{cycle}) = t_{l}Max + t_{d}CQ + t_{s}$$

= 15 + 2 + 3 = [20]

(e) (3) During verification of the design in (d), an engineer found that the DFF hold time is actually longer, t<sub>H</sub>=3. Does this pose a problem? Explain your answer.

(Yes) or No Explain: t<sub>h</sub> ≤ t<sub>c</sub> ca + t<sub>c</sub>M<sub>in</sub> ·:, held time limitation

3 ≤ 1 + 1 3 ≠ 2

(fon(1,15)) (1,15) module, since the hold time is larger than the total contamination delay.

(f) (2) Name as many ways as you can to fix this problem?

- Add à delay on the Winderle that is causing the problem and increase cycle time

- Use a different OFF with a smaller hold time

```

An incomplete Verilog code for a module is shown below:

module final (

input [3:0] st,

output [3:0] nx_st,

input [1:0] in,

output [1:0] out,

input go, reset, done, clock

);

<(a) missing TYPE> [1:0] out;

<(a) missing TYPE> [2:0] nx_st;

always @(<(b) missing activation list>) begin

case (st)

3'b000: nx st=3'b001;

3'b001: nx_st=3'b010;

1. 1

3'b010:

if (in[0] != go)

nx_st=3'b100;

else

nx_st=3'b010;

3'b100:

if (in[0] != go)

nx st=3'b100;

else

nx_st=3'b001;

default:

nx_st = {in[0],1'b0, reset};

endcase

end

assign out[0] = nx_st[1] | in[1];

//(c) out[1] is the output of a mux that selects 1'b0 when reset else nx_st[0]

endmodule

(a) (2) What should be the declared type for the following signals:

autout -[1:0] out;

[2:0] nx_st;

(b) (2) What should go in the activation list of the always @()? Choose only the signals that needs

to be there. You may not use *.

Activation list = posedge clock

(c) (5) The signal, out[1], is the output of a 2:1 MUX that uses input, reset, to choose between

input of 1'b0 (when reset==1), and nx_st[0] (when reset==0). Write the Verilog code for this

signal in three different ways (continue next page):

```

```

// Library module provided

module mux21(muxout, muxselA, inputA, inputB);

// muxselA ==1 chooses inputA

// module details not shown

endmodule

```

10 of 14

UCLA | EEM16/CSM51A | Spring 2018

Declarative Verilog:

$$assign aut [1] = reset : 1'bo : nx_st[0];$$

<u>ল</u>ি

(d) (3) Four different ways of implementing a function is shown below. Which of them are the same? Circle all that are the same.

-

(1)

always (@posedge clock) begin

$$y \le z;$$

$x \le y;$

$y = Z$

$z = y;$

$y = z;$

$x = y;$

$y = z;$

$z = y;$

$y = z;$

$z = y;$

$y = z;$

$z = y;$

$z = y;$

$y = z;$

$z = y;$

$z = y;$

#### UCLA | EEM16/CSM51A | Spring 2018 Question #7 Short Answers (15)

(a) (4) For the following Karnaugh map, the Boolean expression for the function

$$Z = (\neg A \land \neg B \land \neg C) \lor (A \land \neg B \land D) \lor (A \land \neg B \land C)$$

|    |      | AB   |      |      |                   |

|----|------|------|------|------|-------------------|

|    | Z    | "00" | "01" | "11" | "10"              |

|    | "00" | (1)  | 0    | 0    | 0                 |

| CD | "01" | 1    | 0    | 0    | $\left( 1\right)$ |

| CD | "11" | 0    | D    | 0    | (1)               |

|    | "10" | 0    | 0    | 0    |                   |

What input conditions and transition has a potential for causing a glitch (static hazard) at the output?

| Input A transitioning | when | $(A \wedge B \wedge C \wedge D)$ | or (A NBN | $\mathcal{C} \wedge \mathcal{U}$ |

|-----------------------|------|----------------------------------|-----------|----------------------------------|

| can cause a herrard   |      |                                  | ,         |                                  |

(b) (2) How would you resolve the issue in (a) by adjusting the Boolean expression?

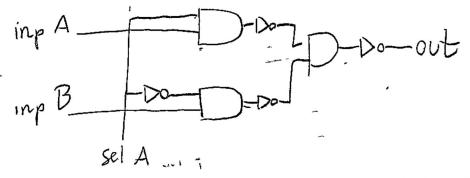

(c) (3) If you only have 2-input AND gates and Inverters available, how would you build a 2:1 multiplexer? (*out* selects between *inpA* and *inpB* with the select signal, *selA*)

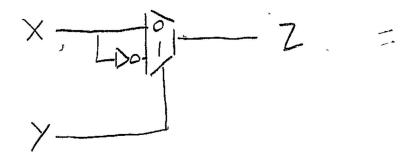

(d) (3) If you only have 2:1 MUX and Inverters available, how would you implement Z = X xor Y?

#### Prof. C.K. Yang

13 of 14

## UCLA | EEM16/CSM51A | Spring 2018

(e) (3) A designer modified the basic DFF as shown below to make a GDFF where the clock signal is ANDed with an Enable signal. This approach is known as "clock gating". How does the GDFF's characteristics compare to that of the DFF? Select the answer.

|                |                      |                              | ect the answer.      |

|----------------|----------------------|------------------------------|----------------------|

|                |                      | GDFF                         |                      |

| Setup:         | ts_gdff > ts_dff     | ts GDFF = ts_DFF             | ts_gdff < ts_dff     |

| Hold:          | th_gdff > th_dff     | $t_{H_{GDFF}} = t_{H_{DFF}}$ |                      |

| Clock-Q Delay: | tc20_GDFF > tc20_DFF | tc2Q_GDFF = tc2Q_DFF         | tc2q_gdff < tc2q_dff |

|                |                      |                              |                      |

|                |                      | i -                          |                      |

|                |                      | ų                            |                      |

|                |                      |                              |                      |

| ,              |                      | ų – v                        |                      |

|                |                      |                              |                      |

|                |                      |                              |                      |

|                |                      |                              |                      |

|                |                      |                              |                      |

|                |                      |                              | ,                    |

|                |                      |                              |                      |

|                |                      |                              |                      |

|                |                      | ,                            |                      |

|                |                      |                              |                      |

|                | ,                    | ļ                            |                      |

|                |                      |                              |                      |

|                |                      |                              |                      |

UCLA | EEM16/CSM51A | Spring 2018 <Extra blank page for work>

ł

Prof. C.K. Yang

•

14 of 14

f