# **EEM16 Midterm**

## Nate Sookwongse

TOTAL POINTS

### 59 / 65

#### **QUESTION 1**

## 1 Problem #1 18 / 18

- √ 0 a) is Correct

- √ 0 b) is correct

- √ 0 c) is correct

- √ 0 d) is correct

- √ 0 e) is correct

- 1 a) added don't cares as minterms

- 3 a) is incorrect

- 2 b) is partially correct

- 5 b) is incorrect

- 3 c) is incorrect

- 3 d) is incorrect

- 2 e) is partially incorrect

- 4 e) is incorrect

- 1 d) partially incorrect

- 2 c) partially incorrect

#### QUESTION 2

#### 2 Problem #2 10 / 14

- 0 all correct

- √ 2 Part (a): answer other than 2, 3 or 4

- √ 1 Part (b): deduct for wrong demorgan

- 0.5 Part(b): partial improper SoP

- √ 1 Part(b): For improper SoP form

- 2 Part(b) quite wrong SoP

- 4 Part(b): all wrong

- 1.5 Part(c): if Not distributive

- 2 Pat(c) no 6 SoP

- 1 Part(c). For each wrong SoP term

- 4 Part(c): all wrong

- 0.5 Part(d): Partial wrong reduced expression

- 1 Part(d): quite wrong reduced expression

- 1 Part(d): For one missing property

- 2 Part(d): For two missing properties

#### **QUESTION 3**

## 3 Problem #3 22 / 22

- √ 0 Correct. Good Job.

- -1 (a) math error

- 2 (a) incorrect

- -1 (a) (b) or (c) math error

- 2 (b) incorrect

- 2 (c) incorrect = -105

- 0.5 (c) negative error for 2's complement

- 2 (d) incorrect hex

- 2 (e) incorrect BCD

- -1 (f) partial credit

- 2 (f) incorrect

- 2 (g) incorrect bias

- 2 (g) incorrect real number

- 1 (g) partial credit for error

- 6 (h) incorrect

- 2 (h) incorrect floating point choice

- -1 (h) partially incorrect min bits for mantissa

- 2 (h) incorrect min bits for mantissa

- -1 (h) partially incorrect min bits for exponent

- 2 (h) incorrect min bits for exponent

## QUESTION 4

### 4 Problem #5 9 / 11

- 0 (a) Correct. Nice Job!

- 7 (a) incorrect

- 5.5 (a) partial for ok attempt

- -3 (a) Too much excessive logic

- 0 (a) No or incorrect Hit logic

### √ - 0.5 (a) Some unnecessary logic

- 0 (b) Correct. Nice Job!

- 4 (b) incorrect

- 3.5 (b) Partial credit for attempt

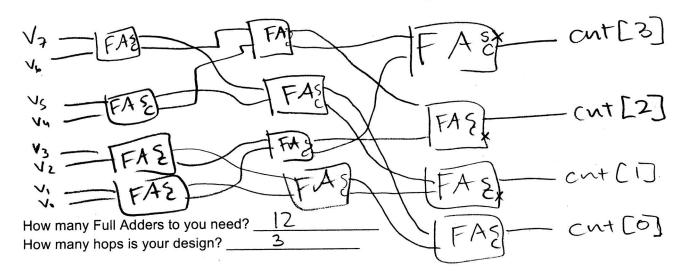

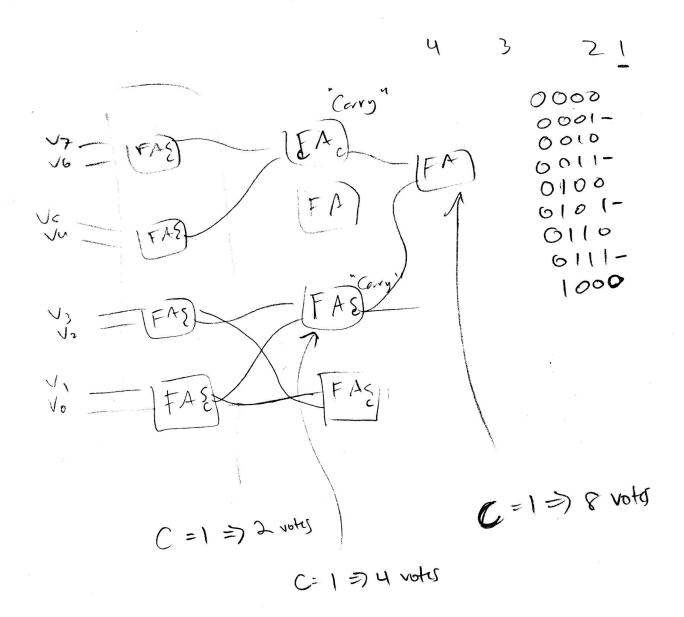

- -1 (b) incorrect bit weight (hop and adder cnt)

- -1 (b) no or incorrect adder count or hop

- **0.5** (b) Good attempt but slightly too many FA

- √ 1.5 (b) ok attempt but incorrect design

- 3 (b) partial credit for attempt

Question #1

Consider the Boolean function defined by the truth table below where A, B, C, and D are inputs, and Y is the sole output.

|            | Y   | D | С   | В | Α   |

|------------|-----|---|-----|---|-----|

| ]-         | 1   | 0 | 0   | 0 | 0   |

|            | 0 ' | 1 | 0   | 0 | 0   |

|            | 0   | 0 | 1   | 0 | 0   |

|            | 0   | 1 | 1   | 0 | 0   |

| ]-         | 1   | 0 | 0   | 1 | 0   |

| <b>-</b>   | 1   | 1 | 0   | 1 | 0 ' |

| <b> </b> - | 1   | 0 | 1   | 1 | 0   |

| ] -        | 1   | 1 | 1   | 1 | 0 . |

| ] -        | 1   | 0 | 0   | 0 | 1   |

| ] •        | 1   | 1 | 0   | 0 | 1   |

|            | 0   | 0 | 1   | 0 | 1   |

| ] 1        | 1.  | 1 | 1 . | 0 | 1   |

| 1          | 0   | 0 | 0   | 1 | 1   |

|            | Х   | 1 | 0   | 1 | 1   |

|            | 1   | 0 | 1   | 1 | 1   |

|            | X   | 1 | 1   | 1 | 1   |

✓(a) Complete the following statements

$$Y = \sum_{m} m(0,4,5,6,7,8,9,11,14)$$

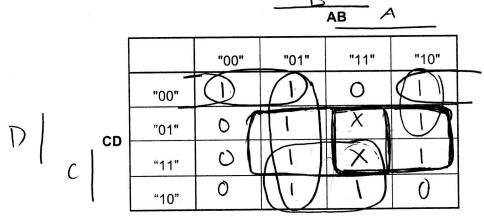

√(b) Complete the Karnaugh Map shown below, circle the prime implicants.

How many prime implicants are there? \_\_\_\_\_\_

✓(c) Write the Boolean (sum-of-product) expression for the essential prime implicants (if any).

EssentialPrimeImplicants =

$$(B^{C})^{V}(A^{D})$$

UCLA | EEM16/CSM51A | Spring 2017

Prof. C.K. Yang

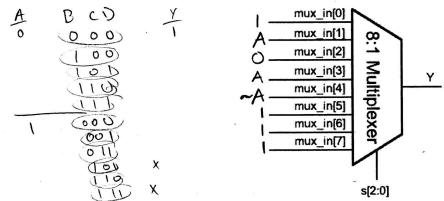

(d) Implement the function Y using an 8-input multiplexer. The select signal is s[2:0]={B,C,D} where s=3'b100 is B=1 and C=D=0 selecting the input mux\_in[4]. A or ~A are permissible as inputs, mux\_in[7:0]. Write the desired inputs on the figure below.

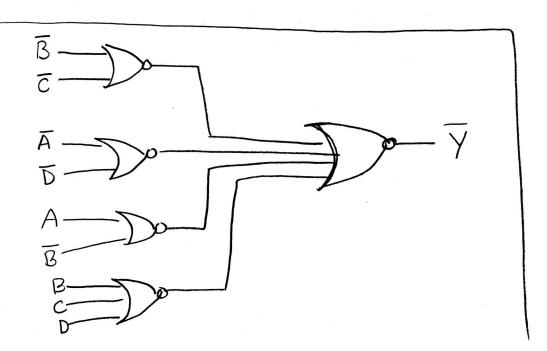

√(e) Implement ¬Y using the minimum # of NOR gates with fewest # of inputs (minimize literals and terms).

Product of SwmS

$$Y = (B \land c) \lor (A \land D) \lor (\overline{A} \land B) \lor (\overline{B} \land \overline{c} \land \overline{D})$$

$$\overline{Y} = (\overline{B} \land \overline{c}) \land (\overline{A} \land \overline{D}) \land (\overline{A} \land \overline{B}) \land (\overline{B} \land \overline{c} \land \overline{D})$$

$$\overline{Y} = (\overline{B} \lor \overline{c}) \land (\overline{A} \lor \overline{D}) \land (\overline{A} \lor \overline{B}) \land (\overline{B} \lor C \lor D)$$

$$\overline{Y} = \overline{(\overline{B} \lor \overline{c})} \lor (\overline{A} \lor \overline{D}) \lor (\overline{A} \lor \overline{B}) \lor (\overline{B} \lor C \lor D)$$

Ouestion #2

$$C \wedge \overline{A} \wedge \overline{e}$$

$$Y = \neg \left( \neg (a \wedge \neg b) \vee \left( c \wedge \neg (d \vee e) \right) \right)$$

- (a) For the above Boolean function, if you were to convert the above expression into a sum-ofproduct representation, how many times did you have to apply DeMorgan's theorem?

- (b) For part (a), what is the resulting function?

$$Y = \frac{\neg (\neg(\alpha \land \neg b) \lor (c \land \neg d \land \neg e))}{}$$

(c) The following expression can be written as a 6-term sum-of-product,

$$Y = (a \lor b) \land (a \lor \neg b \lor \neg c) \qquad \times \not\leftarrow (a + b + c)$$

What Boolean property do you need to apply to do this?

Without reducing, what are the 6 product terms?  $((a \lor b) \land a) \lor ((a \lor b) \land b) \lor ((a \lor b) \lor b$

(d) The 6-term sum-of-product of part (c) can obviously be reduced.

What is the reduced expression?

What Boolean axioms or properties are needed for the reduction?

$$axion \rightarrow a \land a = a$$

$b \land b = 0$

$axions$

$axion \rightarrow a \land a = a$

$b \land b = 0$

$axions$

$axions$

|     | A   EEM16/CSM51A   Spring 2017 Wim Way 0, 25 °C Prof. C.K. Yang estion #3                                                                                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) | The following 8 bits can be used to represent different numbers depending on the encoding 8b'10010111 100 0111  If this was unsigned, what is the corresponding integer? |

| (b) | If the 8 bits in (a) was sign magnitude, what is the corresponding integer?                                                                                              |

|     | If the 8 bits in (a) was 2's complement, what is the corresponding integer? $\frac{-105}{20+2^3+2^5+2^6}$                                                                |

|     | If the 8 bits in (a) was hexadecimal, what is the corresponding hexadecimal?                                                                                             |

| (e) | If the 8 bits in (a) was binary coded decimal, what is the corresponding integer?                                                                                        |

| (f) | If the 8 bits is fixed point 1001.0111, what is the corresponding number? $9.43.75$                                                                                      |

| (g) | If the 8 bits in (a) was a 4E3 floating point number (IEEE format S+EEE+MMMM),                                                                                           |

|     | What is the bias? $3 	 2^{k-1} - 1 = 2^2 - 1 = 3$                                                                                                                        |

|     | What is the corresponding real number? $\frac{-0.359375}{M=1+2^{-2}+2^{-3}+2^{-4}}$                                                                                      |

| (h) | Military temperature range is -55°C to +125°C with 1% accuracy.                                                                                                          |

|     | Would you choose floating point or fixed point? Floating point                                                                                                           |

|     | If you are to represent this in floating point, what is the minimum # of bits for mantissa? $6$ O, 25 °C × 0.01 = 0.0025  Frac 8 b. +5                                   |

|     | And, what is the minimum # of bits for exponent? 4 frac 8 6 145                                                                                                          |

|     | 2×2 <sup>F</sup>                                                                                                                                                         |

|     | E=6                                                                                                                                                                      |

|     | $01 = -2 \qquad exp = \frac{4}{6inS} = 7$                                                                                                                                |

|     | 1.0000,00000 E=6-7                                                                                                                                                       |

|     | E = -2 - Rig                                                                                                                                                             |

exp = -2 + Bing = 5

## UCLA | EEM16/CSM51A | Spring 2017 Question #5

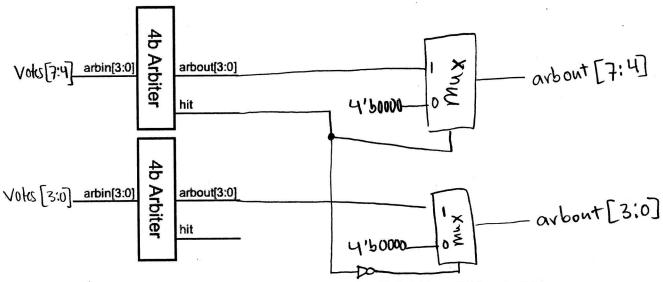

(a) Given 8-bit input, *votes*[7:0], in which any number of the inputs can be a 1'b1. Build an **arbiter** that provides an 8-bit output, *arbout*[7:0], that is 1-hot. The hot signal corresponds to the position with the highest priority. Note that votes[7] has higher priority than votes[6] etc. You have available to you a module ARB that is a 4-bit arbiter already built that you **must** use. ARB accepts as inputs *arbin*[3:0] and outputs *arbout*[3:0] and a *hit* signal to indicate that one or more of the signals is a 1'b1. You also have available to you INV (inverters), and 2-input MUX (multiplexers). Recall that you can implement considerable arbitrary logic with 2-input MUXs.

(b) Now, the *votes*[7:0] need to be counted. You have available Full Adders (FA) as building blocks for implementing a design. If the delay of the logic is determined by the number of hops where each hop is the traversal of a Full-Adder from any input (*a,b,and c*) to any output (*sum, carry*). Design your block to minimize this delay. Note that your design should output 4 bits to indicate the binary count, *cnt*[3:0].

# Blank page for scratch work

Prof. C.K. Yang

UCLA | EEM16/CSM51A | Spring 2017 Blank page for scratch work