University of California, Los Angeles Henry Samueli School of Engineering and Applied Science Department of Electrical Engineering

**D.** Markovic

TuTh 2:00-3:50pm Tuesday, February 13, 6:00-8:30pm

# EE115C: WINTER 07-MIDTERM

| NAME Solution First |

|---------------------|

|---------------------|

|--|

- **Problem 1 (20):**

- **Problem 2 (20):**

- **Problem 3 (20):**

- **Problem 4 (20):**

**Total (80)**

## PROBLEM 1: VTC and IV curves (20 pts)

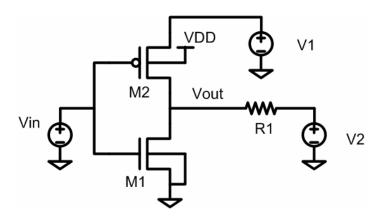

Consider the digital circuit shown in Fig. 1. Use the following MOS parameters.

|      | V <sub>T0</sub> [V] | k' $[\mu A/V^2]$ | $\gamma [V^{1/2}]$ | $\lambda [V^{-1}]$ | V <sub>DSAT</sub> [V] | $2\Phi_{\rm F}\left[{ m V} ight]$ |

|------|---------------------|------------------|--------------------|--------------------|-----------------------|-----------------------------------|

| NMOS | 0.2                 | 90               | 0.1                | 0                  | 0.3                   | -0.6                              |

| PMOS | -0.2                | -40              | -0.15              | 0                  | -0.4                  | 0.6                               |

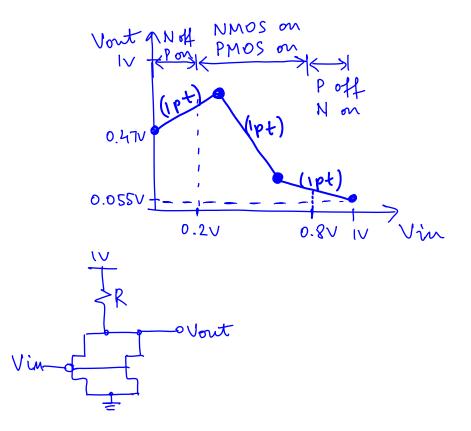

Figure 1: Digital circuit.

The circuit in Fig. 1 is an ordinary CMOS inverter with three DC voltage sources and one resistor. (W/L) of M1 is (240 nm/100 nm), and L of M2 is 100 nm.

a. (8 pts) Student A wants to run simulation with the following settings:

V1 = 1V, V2 = 0, VDD = 1V, and R1 =  $100k\Omega$ . Calculate W of M2 such that V<sub>M</sub> = 0.5V.

$$I_{2} = I_{1} + I_{R} (2p+s)$$

$$V_{GT_{1}} = V_{M} - V_{TO} = 0.3V = V_{DSAT_{1}} M_{1} \quad sat/vel-sat$$

$$V_{DS_{1}} = V_{M} = 0.5V \qquad (1p+t) \\ |V_{GT_{2}}| = 0.3V < |V_{DSAT_{2}}| = 0.4V < |V_{DS_{2}}| = 0.5V = ) M_{2} \quad sat$$

$$40 \left(\frac{W}{L}\right)_{2} \frac{0.3^{2}}{2} = 90.2.4 \cdot \frac{0.3^{2}}{2} + \frac{0.5}{0.1} [MA] \quad (2p+s) \\ \left(\frac{W}{L}\right)_{2} = 8.18 = ) W_{2} = 818 \text{ nm} \quad (2p+s) \\ [OK if you rounded up to 820 \text{ nm} - \text{mfg grid}]$$

W(M2) = 8 | 8 m m

**b.** (12 pts) Student B is curious to find out what happens with the circuit when the values of V1 and V2 are swapped, so he entered the following simulation settings:

V1 = 0, V2 = 1V, VDD = 1V, and  $R1 = 100k\Omega$ .

He doesn't believe the result from (a), so he assumes (W/L) of M2 to be (840nm/100nm).

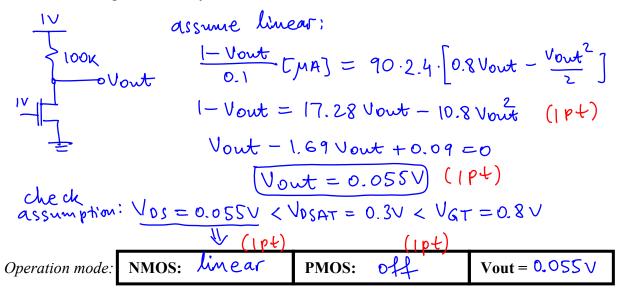

**b1.** (4pts) Find out the value of Vout for Vin = 1V and determine mode of operation for both transistors. Ignore the body effect.

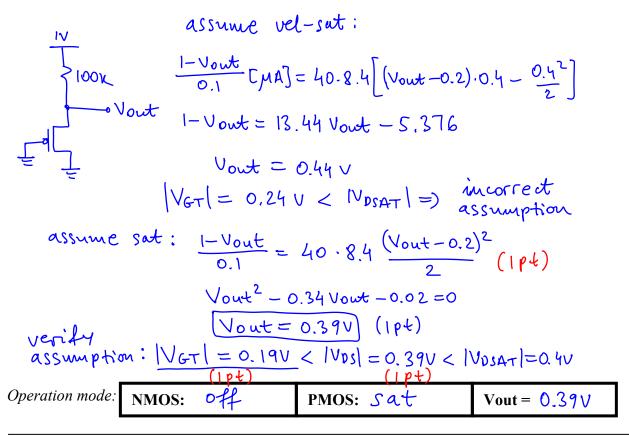

**b2.** (4 pts) Find out the value of Vout for Vin = 0 and determine mode of operation for both transistors. Ignore the body effect.

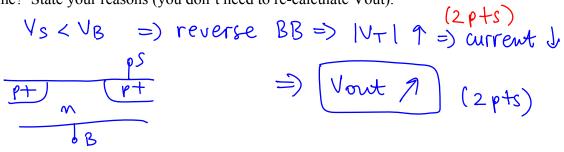

**b3.** (4 pts) If we include body effect in (b2), is Vout going to increase or decrease or stay the same? State your reasons (you don't need to re-calculate Vout).

c. (5 bonus pts / interview question) Student B would definitely get a different VTC from the expected VTC with V1 and V2 properly set. Help out Student B by answering the following:

**c1.** (2pts) Is Vout (Vin = 0.1V) smaller or greater than Vout (Vin = 0)? You don't need to calculate new Vout. Just provide the answer and state your reasons (max 2 sentences).

Circle the correct answer (True/False): Vout (Vin = 0.1V) < Vout (Vin = 0) T (F)Explanation: Smaller  $|V_{GT}| =$ ) Smaller current =) higher Vout (1pt)

**c2.** (3pts) Do a rough sketch of the VTC for student B using piecewise linear approximation with no more than 3 line segments. Roughly indicate the break points.

#### **PROBLEM 2: VTC and propagation delay (20 pts)**

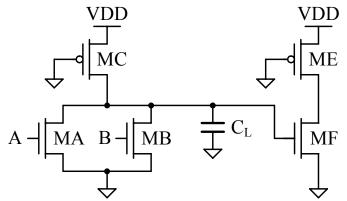

Consider the circuit shown in Fig. 2. It pictures an alternative 2-input NOR gate followed by a single fanout inverter. To make the analysis of this circuit easy, we are using simplified transistor models. First of all, we assume that the transistor can be represented by a linear resistor, this is

NMOS (for W/L = 1):  $RN_{on} = 1 k\Omega$ ;  $RN_{off} = \infty$ ;  $V_{TN} = 0.2V$ .

PMOS (for W/L = 1):  $RP_{on} = 2 k\Omega$ ;  $RP_{off} = \infty$ ;  $V_{TP} = -0.2V$ . VDD = 1V.

Figure 2: Alternative 2-input NOR gate followed by an inverter.

**a.** (6 pts) Assume that the PMOS is of minimum size (this is, W/L = 1). Determine the sizes of the two NMOS transistors MA and MB so that the V<sub>OL</sub> of the NOR gate is **at most** 0.2V. Also describe under what conditions this happens.

worst case: one NMOS "on" (2 pts)

$$\frac{Rn}{Rp} = 0.2 (1 pt)$$

$$\frac{Rn}{Rp + Rp + Rp + Rp + 0.2 Rn}$$

$$\frac{Rn}{Rn} = 0.2 Rp + 0.2 Rn$$

$$\frac{Rn}{L} = 2 (1 pt)$$

$$\frac{Rn}{L} = 2 (1 pt)$$

$$\frac{(1 pt)}{R} \sim \frac{L}{W}$$

$$\frac{(W/L)_{MA}}{R} = 2$$

$$\frac{(W/L)_{MA}}{R} = 2$$

- **b.** (8 pts) The parasitic capacitances of a unit size NMOS and PMOS transistor are given in Table 2. You may assume that all capacitances are constant and linear over the operation range. Determine the equivalent load capacitance  $C_L$  at the output of the NOR gate:

- (i) for A switching from  $0 \rightarrow 1$ , and B = 0;

- (ii) for A and B switching simultaneously from  $0 \rightarrow 1$ .

You should use the sizes derived in (a) for both the NOR gate and the fanout inverter.

**Hint:** In case you are not sure about your answer in (a), use  $(W/L)_{NMOS} = 4$  for all NMOS transistors.

| -                  | Cap in [ | fF]        | $C_{GS}$              | $C_{GD}$  | $C_{GB}$       | $C_{SB}$ | $C_{DB}$                                            |

|--------------------|----------|------------|-----------------------|-----------|----------------|----------|-----------------------------------------------------|

| _                  | NMO      | S          | 0.1                   | 0.15      | 0.2            | 0.25     | 0.3                                                 |

| _                  | PMO      | S          | 0.12                  | 0.18      | 0.22           | 0.27     | 0.32                                                |

| $\sim$             |          | <b>A</b> : | 0→1,B=0               | A,B:0→1   |                |          | 1                                                   |

| 2                  | MA       | 20         | GD+CDB <sup>1.2</sup> | same      | 1.2            |          | ntry = 1pt                                          |

| 2                  |          |            | 50+CDB 0.9            | 2CGD + CI | DB 1.2         | (total = | = 8 p+s)                                            |

|                    | MC       |            | GD + CDB 0.5          |           | 0.5            |          |                                                     |

| 2                  | MF       | Cas        | +CGD+CGB0.4           | same      | 0.9            |          |                                                     |

|                    | Ctot     | 3          | .5 fF                 | 3.8 4     | <sup>2</sup> F |          |                                                     |

| FOR (W/L)NMOS = 4: |          |            |                       |           |                |          |                                                     |

|                    | Ctot     |            | 6.5 fF                | 7.1 ff    | =              |          |                                                     |

|                    |          |            |                       |           | _              |          | $a_{=0} = 3.5 \text{ fF}$<br>$a_{=} 3.8 \text{ fF}$ |

Table 2: Transistor capacitances (for W/L = 1)

c. (6 pts) Determine the propagation delay of the NOR gate for *A* switching from  $0 \rightarrow 1$  and  $1 \rightarrow 0$ , while *B*=0. For *C<sub>L</sub>*, use the answer you got in (b). If not sure, use *C<sub>L</sub>* = 8 fF. You may assume that the V<sub>M</sub> of the gate is approximately at (V<sub>OL</sub> + V<sub>OH</sub>)/2. Assume (W/L)<sub>NMOS</sub> = 4.

$$V_{M} = \frac{V_{0L} + V_{0H}}{2} = b_{0} t_{p} = 0.69 \text{ RC} (1pt)$$

$$\frac{A: 0 \rightarrow 1, B=0}{V_{0ut}: 1 \rightarrow 0}$$

$$R = Rm || Rp = 0.25k || 2k = 0.22k (2 pts)$$

$$t_{pHL} = 0.69 \cdot 0.22k \cdot 8f = 1.23 \text{ ps} (1pt)$$

$$\frac{A:1 \rightarrow 0, B=0}{V_{0ut}: 0 \rightarrow 1}$$

$$R = Rp = 2k (1pt)$$

$$t_{pLH} = 0.69 \cdot 2k \cdot 8f = 11.04 \text{ ps} (1pt)$$

$$t_{pLH} = 1.23 \text{ ps}$$

$$t_{pLH} = 1.04 \text{ ps}$$

## **PROBLEM 3:** Wire modeling (20 pts)

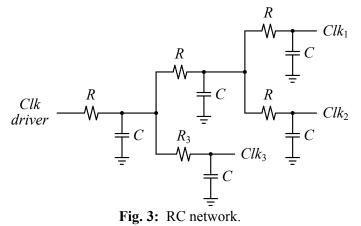

a. (8 pts) Consider *RC* network shown in Fig. 3.

**a1.** (6pts) Write expressions for the time constants associated with  $Clk_1$ ,  $Clk_2$ , and  $Clk_3$ . Write your final answer in terms of RC parameters.

$$\mathcal{Clk}_{1} \& \mathcal{Ll}_{2} \text{ are symmetric} \Rightarrow \mathcal{T}_{1} = \mathcal{T}_{2} \quad (2p+s)$$

$$\mathcal{T}_{1} = \mathcal{T}_{2} = RC + 2RC + RC + 3RC + 2RC = 9RC \quad (2p+s)$$

$$\mathcal{T}_{3} = RC + RC + RC + RC + (R+R_{3})C = 5RC + R_{3}C \quad (2p+s)$$

| $\tau_1 = 9 RC \qquad \tau_2 = 9 RC$ | $\tau_3 = 5RC + R_3C$ |

|--------------------------------------|-----------------------|

|--------------------------------------|-----------------------|

**a2.** (2pts) What value of  $R_3$  (in terms of R) is required to balance the delays to  $Clk_1$ ,  $Clk_2$ , and  $Clk_3$ ?

$$9RC = 5RC + R_3C \quad (1Pt)$$

$$R_3 = 4R \quad (1Pt)$$

$$R_3 = 4 R$$

**b.** (6 pts) Assume that the resistances in Fig. 3 are voltage-dependent:  $R = 0.8 R_0 / (V_{DD} - V_{TH})$ , where  $R_0$  is the nominal value at  $V_{DD} = 1V$ , and  $V_{TH} = 0.2V$ .

**b1.** (3 pts) Calculate energy-delay-product (in terms of  $R_0$ , C,  $V_{DD}$ , and  $V_{TH}$ ), where energy is equal to the total energy expended during a complete  $0 \rightarrow 1$  transition at the Clock driver input.

$$E_{0\to1} = 5C V_{DD}^{2} \quad (1pt)$$

$$t_{P} = 0.69 \cdot 9C \cdot \frac{0.8 R_{0}}{V_{DD} - V_{T}} \quad (1pt)$$

$$EDP = 24.84 C^{2}R_{0} \frac{V_{DD}^{2}}{V_{DD} - V_{T}}$$

$$EDP = 24.84 C^{2}R_{0} \frac{V_{DD}^{2}}{V_{DD} - V_{T}}$$

**b2.** (3 pts) Find the optimal supply voltage  $V_{DD}$  that minimizes the energy-delay product.

$$\frac{2 \text{EDP}}{2 \text{VDD}} = \frac{2 \text{VDD} (\text{VDD} - \text{VT}) - \text{VDD}^{2}}{(\text{VDD} - \text{VT})^{2}} = 0 \quad (2\text{P+S})$$

$$\frac{\text{VDD}}{(2\text{P} + \text{VT})^{2}} = 0 \quad (2\text{P+S})$$

$$\frac{\text{VDD}}{(2\text{P} + \text{VT})^{2}} = 0 \quad (2\text{P} + \text{VT})$$

$$\frac{\text{VDD}}{(2\text{P} + \text{VT})^{2}} = 0 \quad (2\text{P} + \text{VT})$$

c. (6pts) Consider an isolated 1mm long and 1µm wide Metal-1 wire over a silicon substrate driven by an inverter with zero output resistance and zero capacitance. Assume  $C_{pp} \approx C_{fringe}$ .

**c1.** (3 pts) If the wire width is doubled, the delay of this wire will be (circle one):

More than  $2 \times$  shorter Less than doubled

Exactly  $2 \times$  shorter Exactly doubled

Unchanged

Shorter, but less than  $2\times$ More than doubled (10+)

Explanation:

$R \sim \frac{L}{W}, Cpp \sim W, Cfr \neq f(W) \qquad \frac{R}{2} \left[ 2Cpp + Cfr \right] (1pt)$

c2. (3 pts) If the wire length is halved, the delay of this wire will be (circle one):

More than 2× shorter (1pt)

Exactly 2× shorter Exactly doubled

Shorter, but less than  $2 \times$ More than doubled

Explanation: (1P+)  $R \sim \frac{L}{W}$ ,  $C_{PP} \sim L$ ,  $C_{Fr} \sim L$   $\frac{R}{2} \left[ \frac{C_{PP}}{2} + \frac{C_{Fr}}{2} \right]$  (1P+)

Less than doubled

Unchanged

#### **PROBLEM 4:** General Knowledge (20 pts)

--

**a.** (10 pts) Determine the region of operation (Off, Linear, Saturation, Velocity saturation) in the following configurations. You may assume that all transistors are **short-channel devices** and have identical sizes,  $V_{DD} = 1V$ . Assume following transistor parameters:

NMOS:  $V_{Tn} = 0.2V$ ,  $k_n' = 90\mu A/V^2$ ,  $V_{DSATn} = 0.3V$ ,  $\lambda = 0$ ,  $\gamma = 0.1V^{1/2}$ ,  $2\Phi_F = -0.6V$ PMOS:  $V_{Tp} = -0.2V$ ,  $k_p' = -40\mu A/V^2$ ,  $V_{DSATp} = -0.4V$ ,  $\lambda = 0$ ,  $\gamma = -0.15V^{1/2}$ ,  $2\Phi_F = 0.6V$

Explain your reasoning and show your derivations if needed.

$$V_{DD}$$

$$V_{GS1} = V_{DS1} = -1V$$

$$|V_{DSAT1}| < |V_{GT1}| < |V_{DS1}| \Rightarrow M_1 \text{ velocity saturation} \qquad (2 \text{ pts})$$

$$V_{DD} \xrightarrow{V_{DD}} M_{2}$$

$$V_{GS3} = 0 < V_{T3} \Rightarrow M_{3} \text{ off}$$

$$V_{x} = V_{DD} - V_{T2} \Rightarrow M_{2} \text{ off}$$

(2 pts)

(2 pts)

$$V_{DD} \xrightarrow{V_{DD}} V_{T4} > V_{T5} \text{ (body effect)} \Rightarrow V_{DS5} < V_{GT5} \Rightarrow M_5 \text{ linear} (2 \text{ pts})$$

$$Assume M_4 \text{ vel sat and ignore body effect in the first iteration:}$$

$$(V_{DD} \xrightarrow{M_5} (V_{DD} - V_{T4}) \cdot V_x - \frac{V_x^2}{2} = (V_{DD} - V_x - V_{T5}) \cdot V_{DSAT} - \frac{V_{DSAT}^2}{2}$$

$$V_x = 0.195 \text{V} \Rightarrow M_4 \text{ velocity saturation} (2 \text{ pts})$$

Note: Body effect will only lower  $V_x$  and increase  $V_{DS4}$ ,  $V_{GT4}$  (0.195V is the worst-case).

**b.** (6 pts) The power consumption of the CMOS inverter can be minimized through circuit optimizations. Determine how each circuit parameter mentioned in the table should be changed to reduce the different inverter power consumption components.

### For each parameter, fill in one of the following choices in the blanks:

A – Increase **B** – Decrease  $\mathbf{C}$  – Doesn't affect this type of power consumption

| Goal                                                          | Circuit Parameter Optimization  | A, B or C |

|---------------------------------------------------------------|---------------------------------|-----------|

|                                                               | Supply voltage $V_{DD}$         | B         |

| Minimize the <b>dynamic power</b>                             | Load capacitance C <sub>L</sub> | B         |

| consumption due to C <sub>L</sub><br>charging and discharging | Transistor  V <sub>TH</sub>     | С         |

|                                                               | Transistor width (first order)  | С         |

| Minimize the <b>short-circuit</b>                             | Supply voltage V <sub>DD</sub>  | В         |

| <b>power</b> consumption (assume a                            | Load capacitance C <sub>L</sub> | A         |

| fixed rise and fall time at the input)                        | Transistor $ V_{TH} $           | A         |

|                                                               | Transistor width (first order)  | В         |

|                                                               | Supply voltage V <sub>DD</sub>  | В         |

| Minimize the leakage power                                    | Load capacitance C <sub>L</sub> | С         |

| dissipation                                                   | Transistor $ V_{TH} $           | A         |

|                                                               | Transistor width (first order)  | B         |

each entry = 0.5 pts(total = 6 pts)

c. (4 pts) For each of the statements, indicate whether it is true or false (circle one answer).

(0.5 pts) (T) F (a) The load capacitance of a static CMOS gate has no effect on its VTC. Explanation: NO Static Current dependence of a static CMOS gate has no effect on its VTC. Explanation: no static current through C (0.5 pts)

(O.Sph)T (E) (b) The delay of a static CMOS inverter is minimized if  $(W/L)_p / (W/L)_n = \mu_n / \mu_p$ . Explanation:  $tp_{HL} = tp_{LH}$ , but  $tp = awg(tp_{LH}, tp_{HL})$  not min (0.5ph)

(0.5pk)T (c) Silicided poly lines improve performance by decreasing the capacitance. Explanation: performance improved by RJ (0.5 pts)

$(0.5 \beta b)T$  (**F**) (d) PMOS enters vel. saturation for smaller absolute value of electric field than NMOS. Explanation: /p < Mn =) higher VOSATP => higher [Earitp] (0.5 pts