## **UCLA**

Department of Electrical Engineering

EE10 Midterm 1

Spring 2011

Instructor: Prof. Gupta

April 25<sup>th</sup>, 2011

- 1. Exam is closed book. You are allowed one 8 ½ x 11" single-sided cheat sheet.

- 2. Calculators are allowed.

- 3. Cross out everything that you don't want me to see. Points will be deducted for everything wrong!

Name:

Student ID:

Student on Left:

Student on Right:

Student in Front:

| Problem | Maximum Score | Your Score |

|---------|---------------|------------|

| 1       | 10            |            |

| 2       | 6             |            |

| 3       | 4             |            |

| 4       | 3             |            |

| 5       | 2             |            |

| Total   | 25            |            |

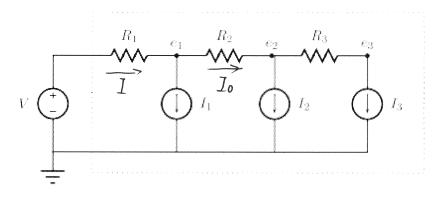

Q1. (10 points) The dotted line below shows a model for power distribution network of a typical processor. The voltage source models the external supply that powers the processor, the resistors model the power distribution wiring internal to the processor, and the current sources model the loads presented by the individual parts of the processor. The source values V, I1, I2 and I3 are all positive, as are the three internal node voltages e1, e2 and e3. Further, depending upon whether the corresponding part of the processor is in use or not, I1, I2 and I3 can each take on only the value of either I or zero.

(a) Using the node method, develop a set of simultaneous equations for the power distribution network that can be solved for the three unknown node voltages e1, e2 and e3. Express these equations in the form (5 points)

$$G \begin{bmatrix} e1 \\ e2 \\ e3 \end{bmatrix} = S$$

where G is a  $3 \times 3$  matrix of conductance terms and S is a  $3 \times 1$  vector of terms involving the sources V, I1, I2 and I3. You need not solve the set of equations for the node voltages.

$$G = \begin{bmatrix} \frac{1}{R_1} + \frac{1}{R_2} & -\frac{1}{R_3} & 0 \\ -\frac{1}{R_2} & \frac{1}{R_3} + \frac{1}{R_3} & -\frac{1}{R_3} \\ 0 & -\frac{1}{R_3} & \frac{1}{R_3} \end{bmatrix}$$

$$S = \begin{bmatrix} \frac{1}{R_1} - I_1 \\ -I_2 \\ -I_3 \end{bmatrix}$$

(b) Given the possible values for I1, I2 and I3, what is the maximum power that the voltage source must be able to supply to the processor? Express your answer in terms of V, I, R1, R2 and R3. (5 points)

$$P_V = V \cdot I = V(J_1 + J_2 + J_3)$$

therefore the maximum proveer is given by.

Q2. (6 points) Find the equivalent inductance seen at terminals 1 and 2 in the network of the figure below if the following terminals are connected together:

100 none are connected together

$$V(t) = 5 \frac{di(t)}{dt} - 3 \frac{di(t)}{dt}$$

$$V_{1}(t) = 5 \frac{di(t)}{dt} - 3 \frac{di(t)}{dt}$$

$$V_{2}(t) = 2 \frac{di(t)}{dt} - 3 \frac{di(t)}{dt}$$

$$V_i(t) = 5 \frac{dirt}{dt} - 3 \frac{dirt}{dt}$$

$$V(t) = 5 \frac{di(t)}{dt} - 3 \frac{di(t)}{dt} = 5 \frac{di(t)}{dt}$$

$$\Rightarrow 5i(t) - 3i(t) = 5i(t)$$

$$V(t) = 5 \frac{di(t)}{dt} = 5 \frac{di(t)}{dt}$$

$$V(t) = 5 \frac{di(t)}{dt} = 5 \frac{di(t)}{dt}$$

$$V(t) = 5 \frac{di(t)}{dt} = 5 \frac{di(t)}{dt}$$

Therefore

$$V(t) = V_1(t) + V_2(t) = 5 - \frac{diz(t)}{dt} + 2 - \frac{dirt}{dt} - 3 - \frac{dirt}{dt}$$

$$= \frac{dirt}{dt} + 2 \frac{dirt}{dt} - 3 + \frac{dirt}{dt} = \frac{3}{5} \frac{dirt}{dt} = \frac{3}{5} \frac{dirt}{dt}$$

$$= \frac{3}{5} + \frac{3}{5}$$

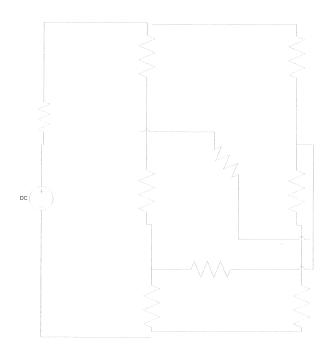

Q3. (4 points) Draw the graph of this circuit (after zeroing the voltage source). Is it planar? Will it be better to solve it using node method or loop method?

Since the circuit cannot be drown on a sheet of paper without coossing lines. it is nonplanar

N=6 b=9 i'n the graph. Needs n-1=5 equations in node method while needs b-n+1=9-6+1=(0-6=4) equations in loop method. Therefore it is better to solve by loop method Q4. (3 points) You solve some circuit using loop method and after an hour of calculations, you wrote down the matrix equations corresponding to it but unfortunately you spilled coffee on the piece of paper. As a result only part of the equations is visible:

$$\begin{bmatrix} v1 \\ v2 \\ v3 \\ v4 \end{bmatrix} = \begin{bmatrix} 1 & -3 & -8 & -2 \\ 4 & & -7 \\ -1 & 9 & & i3 \\ & -5 & 2 & i4 \end{bmatrix} \begin{bmatrix} i1 \\ i2 \\ i3 \\ i4 \end{bmatrix}$$

What do you need to assume to fill in the remaining entries in the matrix? In this case, fill in the remaining entries.

Assume in the absence of control sources. we can fill the matrix by symmetry

$$\begin{bmatrix}

1 & -3 & -8 & -2 \\

-3 & 4 & -1 & -7 \\

-8 & -1 & 9 & -5 \\

-2 & -7 & -5 & 2

\end{bmatrix}$$

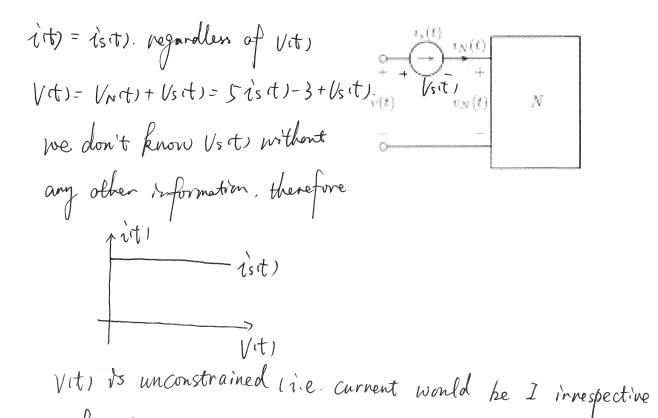

Q5. (2 points) What is the v-i relationship at the input of this circuit? The network N obeys the  $v_n(t) = 5i_n(t)$  -3.