Problem No. 1 (10 points)

Part (a) An electric garage door opener *iLock* uses a small radio transmitter that sends a 5-bit sequence to a receiver inside the garage to open the door, and each receiver is supposed to respond to a different sequence. Suppose you live on a street with 40 houses, each using the same model of the opener.

Show your work below for full credit:

$$2^{5}=32$$

.

(a.2) Suppose a burglar Digi Hak wants to break into one specific garage using this type of opener. If he has a transmitter which can send different 5-bit sequences, at least how many times he needs to try before he breaks into any particular garage?

Answer: 31

Show your work below for full credit:

Part (b) Length can be measured by one 3-digit weighted mixed-radix number system (yards, feet, inches). The relationships between weights of each digit of this number system are: 1 yard = 3 feet, 1 foot = 12 inches. Assume that radix for the yard's digit is ten.

2.5pts (b.1) What is the largest number of inches that this number system can represent?

Answer: 359 inches

(b.2) How many inches are represented by the digit vector X = (8, 2, 9)?

Answer: 321 inches

Show your work below for full credit:

(b.1)

$$X_{\text{max}} = (9, 0.11)$$

$\Rightarrow X_{\text{max}} = 9 \times 3^{12} + 0.12 + 11 = 359$

or:  $X_{\text{max}} = 10 \times 3 \times 12 - 1 = 359$

(b.2)  $X = 8 \times 3 + 0.12 + 9 = 321$

Problem No. 2 (10 points)

A high-tech startup HotCom, Inc. is operated by CEO A, CFO B, and two members of the Board of Directors, C and D.

To make a decision, A needs support from at least another board member, while B needs support from at least two other board members.

Part (a) bpts.

Fill in the truth table of function F below. F = 1 if and only if a decision has been approved.

| A | В | C | D | F |  |

|---|---|---|---|---|--|

| 0 | 0 | 0 | 0 | 0 |  |

| 0 | 0 | 0 | 1 | 0 |  |

| 0 | 0 | 1 | 0 | 0 |  |

| 0 | 0 | 1 | 1 | 0 |  |

| 0 | 1 | 0 | 0 | 0 |  |

| 0 | 1 | 0 | 1 | 0 |  |

| 0 | 1 | 1 | 0 | 0 |  |

| 0 | 1 | 1 | 1 | 1 |  |

| 1 | 0 | 0 | 0 | 0 |  |

| 1 | 0 | 0 | 1 | 1 |  |

| 1 | 0 | 1 | 0 | 1 |  |

| 1 | 0 | 1 | 1 | 1 |  |

| 1 | 1 | 0 | 0 | 1 |  |

| 1 | 1 | 0 | 1 | i |  |

| 1 | 1 | 1 | 0 | 1 |  |

| 1 | 1 | 1 | 1 | 1 |  |

Part (b) 4 h

(b.1) Write the minterm expression for F(A, B, C, D) in compact form:

$$F(A, B, C, D) = \sum_{m} \{7, 9, [0, 1], [2, 13, [4, 15]]\}$$

(b.2) The switching expression for maxterm  $M_8$  is:

$$M_8 = A' + B + C + D$$

Problem No. 3 (10 points)

Your high school buddy BB Fred is interviewed for an internship position at a startup Kookle Electronics. One of his interview questions is the tabular minimization using the Quine-McCluskey algorithm for the following 4-input switching function:

$$f(a, b, c, d) = \sum m(4, 5, 6, 8, 9, 10, 13) + \sum d.c.(0, 7, 15)$$

BB Fred has completed the first step and the Prime Implicant Chart is shown below. You have to help him identify the essential prime implicants and then write the minimal AND-OR (sum-of-product) expression for f(a, b, c, d).

Prime Implicant Chart Minterms Prime Implicants 0 - 00-000100 -10 - 0E 1 - 0101 - -E -1 - 1

1913 Part (a) The essential prime-implicants in switching expressions are:

Part (b) The minimal switching expression in AND-OR form is:

$$f(a,b,c,d) = ab'd' + a'b + ac'd$$

Show all your work on the prime implicant chart above for full credit.

Problem No. 4 (15 points)

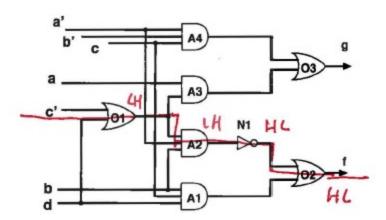

Given the gate network below, answer the following questions:

Part (a) Assuming that negated variables are available and that all gates have the same delays, identify the *critical path* of the network by listing its gates along the path, starting at the inputs:

Part (b) Assuming that load factors of all gates equal to 1 and that both outputs f and g have the output load value L, list the output load value of every gate in the critical path (e.g., A1: 1):

Part (c) Write the expression of the longest network propagation delay  $T_{pHL}$  in terms of delays of each gate (You do not need to compute the final result but the transition direction at each gate has to be indicated):

Part (d) Assuming that negated variables are available, find the switching expression of the output f in two-level AND-OR (sum-of-product) form. It does not have to be minimal. Show your work below for full credit.

$f(a,b,c,d) = \frac{a+b'+cd'+bcd}{+bcd'+bcd}, \text{ or } a+cd+cd'+b', \text{ or } a+b'+c$ Your work for Part (d): f = (a'b(c'+d))'+bcd = a+b'+(c'+d)'+bcd = a+b'+cd'+bcd = a+cd+cd'+b' = a+cd+cd'+b'

Your SID:

Problem No. 5 (15 points) Office as bone,

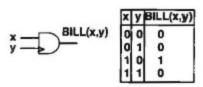

Armed with a solid A in Spring 2014 CS M51A/EE M16 class, Elsa has easily landed a job as a digital system design engineer in SuperLogic after graduation. She is motivated to revolutionize the logic design and has invented a new type of logic gate, called BILL gates. Its symbol and truth table are given below.

800 Part(a) Is the BILL gate a universal set?

Show all your work below for full credit.

@ From the truth table.

Bill(x,y) = xy'.

: , BILL (1,4) = y1 -> NoT gate.

@ BILL(x,y1)=xy

. BILL (26, BILL(1,41) = x4 -> AND gate.

.. But gates can implement (NOT. AND), which is a universal cet.

(Continue on the next page)

## (Continue from Problem No. 5)

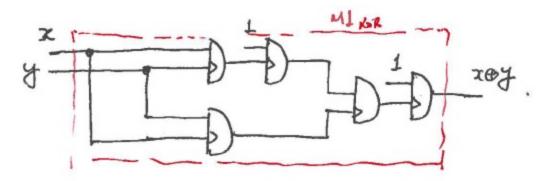

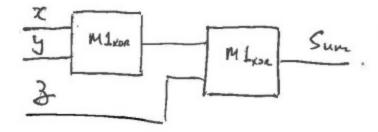

Part(b) If the answer in Part (a) is yes, draw a network that implements the sum of a 1-bit full adder using only BILL gates; If the answer is no, draw a network that implements the sum of a 1-bit full adder using BILL gates and any other types of gates as needed.

Show all your work below for full credit.

an & xor gate is implemented with Bicc gates as follows (MI)

.. Sun can be implemented as

Problem No. 6 (15 points)

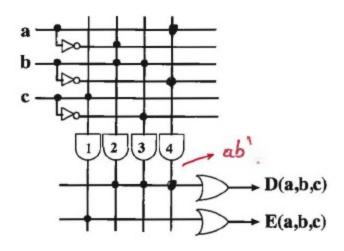

A junior engineer Goofy is assigned to design a digital circuit using one PLA. The circuit converts a 3-bit 2's complement number *abc* into its 2-bit absolute value (unsigned integer) *DE*. He works out a minimal design and implements it on the PLA as shown below. Regrettably, he makes <u>ONE SINGLE MISTAKE</u> in the design. As a result, the circuit <u>DOES NOT</u> work correctly.

Your task is to help Goofy:

- 1. Debug the design and find the error. Show all your work in the provided space below.

- Correct the error by adding and/or removing connections on the original PLA diagram above. Use a "X" for a connection removed and a heavy dot "•" for a connection added. Your correction <u>MUST BE MINIMAL</u>.

(Extra space available on the next page)

(Extra space for Problem No. 6)

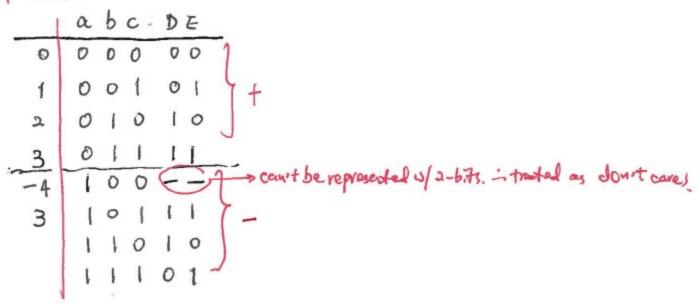

5 pts Step 1: The truth table is:

$$\cdots D = a'b + bc' + ab'$$

$E = c$

E

5th Step3. Compare Goofy's design from PLA implementation D=ab+bc'

$$E = c$$

is Goofy missed the term ab. fixed as shown in 74

(End of Problem No. 6)

Problem No. 7 (15 points)

Fill in blanks in the following table by performing conversions and arithmetic operations in specified binary number systems. For one's complement and two's complement in parts (c) and (d), use only complementation and addition, and indicate overflow if it occurs. For part (e), use only range extension, shifting, complementation, and addition as needed, and no subtraction, multiplication, or division is allowed. Use provided space for all your work and clearly LABEL your steps and the final answer.

| lphfor    | Operations |                          | Sign/Magnitude |         | 1's Complement |         | 2's Complement |         |

|-----------|------------|--------------------------|----------------|---------|----------------|---------|----------------|---------|

| por       |            |                          | Bit            | Signed  | Bit            | Signed  | Bit            | Signed  |

| Volode.   |            |                          | Vector         | Integer | Vector         | Integer | Vector         | Integer |

| 2 pis P   | art (a):   | x                        | 10100          | -4      | 10100          | -11     | 10100          | N/A     |

| y 4 2pt P | art (b):   | у                        | 01011          | +11     | 01011          | N/A     | 01011          | +11     |

| L 2pts. P | art (c):   | s = x + y                | N/A            | N/A     | 11111          | -0      | N/A            | N/A     |

| 4 pts P   | art (d):   | d = x - y                | 11111          | -15     | N/A            | N/A     | ovan Z(        | ow      |

| Spts. P   | art (e):   | $z = -\frac{3}{2}x + 7y$ | N/A            | N/A     | N/A            | N/A     | 1000000        | -64     |

a serell. Show all your work below for full credit.

Part (b): y

(Continue on the next page)

(Continue from Problem No. 7)

Part (c):

$$s = x + y$$

Part (d):

$$d = x - y$$

(Continue on the next page)

(Continue from Problem No. 7)

Part (e):  $z = -\frac{3}{2}x + 7y$

@ Raye extersion:

(End of Problem No. 7)

Problem No. 8 (10 points)

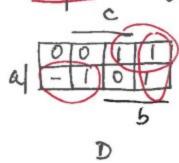

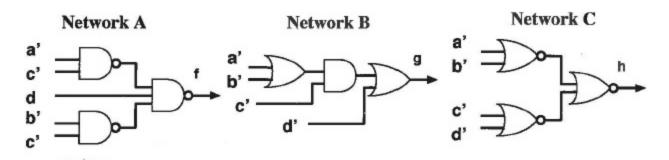

Three gate networks A, B and C are given below. Tests have shown that two of them are equivalent, that is, they implement the same switching function. You are asked to identify the network that is not equivalent.

Part (a) Describe in one sentence your approach.

Answer: 3 use K-map

De use truth table

Part (b) The non-equivalent network is

Show all your work below for credit:

Method L: f = a'c'+d'+b'c' g = (a'+b')c'+d'=a'c'+d'+b'c' h = (a'+b')(c'+d') = a'c'+a'd'+b'c'+b'd' $\Rightarrow$  Network C is different

(End of Midterm)