## Name:

## Midterm Exam, CS151B/EE116C, Spring 2007

Andrew Ackerman

28

## General Guidelines:

- You can use the required textbook (including a printout of appendices), printouts from the class web page, and a calculator. NOTHING ELSE.

- Using notes or textbooks with solutions to homework/example/old-exam problems is CHEATING.

- You must return the exam with the answers on the exam pages.

- Always make sure that you provide an explanation or justification for your answer and clearly state all your assumptions.

- Produce clear, well-organized answers! Points will be taken off for disorganized messy writing.

- Unless specified otherwise, when writing MIPS assembly code, you <u>must</u> use <u>only</u> the \$reg-number notation (e.g., \$22, \$5) to specify a register. Any other notation will be considered incorrect.

- $1K = 2^{10} = 1024$ ,  $1M = 2^{20} = 1,048,576$

- Just in case you need it:  $2^4 = 16$ ,  $2^8 = 256$ ,  $2^{16} = 65536$ ,  $2^{20} = 1048576$ ,  $2^{32} = 4294967296$

(1) Write your name at the top of this page and every other page not stapled to this page.

22

(2) This problem deals with the multicycle MIPS implementation described in chapter 5 of the textbook. In the following table each row refers to a control signal (or related set of control signals) that are used in this implementation. Consider the \(\perp \widetilde{W}\) instruction. For each signal in the table list \(\frac{\partial \text{II}}{\partial \text{I}}\) the cycles during which the signal can be either 0 or 1 without having any impact on correct operation, i.e., the signal is a "don't care".

The notation that you <u>must</u> use is that 1 denotes the first cycle (state 0), 2 denotes the second cycle, 3 denotes the third cycle, etc. If the signal value is important in every cycle (i.e., it is never a "don't care"), write NONE.

22/22

| Signal   | Cycles of 1w during which the signal is a "don't care" |

|----------|--------------------------------------------------------|

| PCSource | 2,3,4,5                                                |

| RegDst   | 1, 2, 3, 4                                             |

| MemWrite | None                                                   |

| ALUOp    | 4,5                                                    |

| MemtoReg | 1, 2, 3, 4                                             |

| PCWrite  | None                                                   |

(3) The following recursive C function sums up the elements of an array.

```

int sum( int arr[], int size ) {

if ( size == 0 )

return 0 ;

else

return sum( arr, size - 1 ) + arr[ size - 1 ] ;

}

```

Below is a MIPS translation of the program. Some of the instruction fields are missing (indicated by underlines). Fill in the missing instruction fields with the correct values.

Assume that arr is in \$a0 and size is in \$a1.

For this problem, you should use the symbolic names for registers: \$t1, \$a3, etc.

|     | Name:             | 4 OA             | (U)           |           | 400            | W2D                     |               |              |

|-----|-------------------|------------------|---------------|-----------|----------------|-------------------------|---------------|--------------|

|     |                   | 508              |               | ÐΚ        | 50C            | V                       | c?m           | 1.5B         |

|     |                   | OD               | L513          |           | 7.0 A          | LSB                     | •             | -            |

|     | (4) Before the fo | llowing code se  | gment is ex   | xecuted,  | register \$9 ( | contains the            | value UXUAUBU | <u>CUD</u> . |

| (8) |                   | sw               | \$9,4(        | \$0)      |                |                         |               |              |

| ,   | •                 | (lb)             | \$8,5(        |           |                |                         |               |              |

| 8/8 | What is the v     | alue in register | \$8 after the | e code se | egment is ex   | ecuted?                 |               |              |

| 10  | Big Endian r      | nachine: O       | (OB           | 1         | Little Endia   | n machine: <sub>-</sub> | Ox OC         |              |

|     | Dig Dilaimi i     |                  |               |           |                |                         |               |              |

(5) Consider the multicycle MIPS implementation shown in Figure 5.28 (page 323) and Figure 5.38 (page 339). Assume that the control unit is implemented using the PLA shown in Figure C.3.9 (page C-20). The following table summarizes the delays of the various components of this implementation:

| module                                                   | delay in nano seconds |

|----------------------------------------------------------|-----------------------|

| ALU latency                                              | 20                    |

| Adder latency                                            | 18                    |

| latency of PLA in control unit                           | 9 <                   |

| latency of ALU control                                   | 5                     |

| MUX latency (all MUXes)                                  | 4                     |

| memory read latency                                      | 22                    |

| memory write latency (setup time)                        | 23                    |

| register file read time                                  | 11                    |

| register file setup time                                 | 9                     |

| setup time of the flip-flops in all individual registers | 4                     |

| hold time of the flip-flops in all individual registers  | 3                     |

| clock-to-Q of the flip-flops in all individual registers | 3 —                   |

| AND gate latency                                         | 1                     |

| sign extender latency                                    | 1.5                   |

| Shift left 2 latency                                     | 0.9                   |

Note: The parameters for the "individual registers" do not apply to the register file.

The latency of each one of the wires explicitly shown in Figure 5.28 is 0.5ns. The latency of wires not explicitly shown in Figure 5.28 is 0. Note: you must take these wire delays into account in your calculation. Symbolically, specify the wire delay using WDel.

Assume that the **fifth** cycle of the 1w instruction determines the constraints on the cycle time. Your task is to determine the minimum cycle time of the design.

You **must** derive a precise expression for the cycle time using symbols before plugging in the numbers and computing the minimum cycle time in nano-seconds. For the expression, follow the example on pages 5.18 and 5.19 in the notes. You must provide **both** the symbolic expression and the final numerical result.

Write your answer on the next page. The complete answer must fit on the next page.

Name: Keystes Setuption + max Monthum Tycle - Registes Solup time + Wale / + /4 tency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Wale / + Months me + Mux lixency of PIA in Control + Months me + Mux lixency of PIA in Control + Months me + Mux lixency of PIA in Control + Months me + Mux lixency of PIA in Control + Months me + Mux lixency of PIA in Control + Months me + Mux lixency of PIA in Control + Months me Note: all misses have equal latercy, latercy of Pla in Control > Clack to Q of FF ". Martin Pcycle - 2.5 5 15 4 9 1 9 = with late | wole / + mux letercy of Write Date + max / letroy of Pla in commo! + wole / /s feter reger! ludel + mux laterey of Witches + from Throng of MAIN control + widel + state ing czg / Wdel + Clock to Q of MDR Robot Letony of Pla in control + water + state - 1.09 c21 Spring 2007, YT (33)

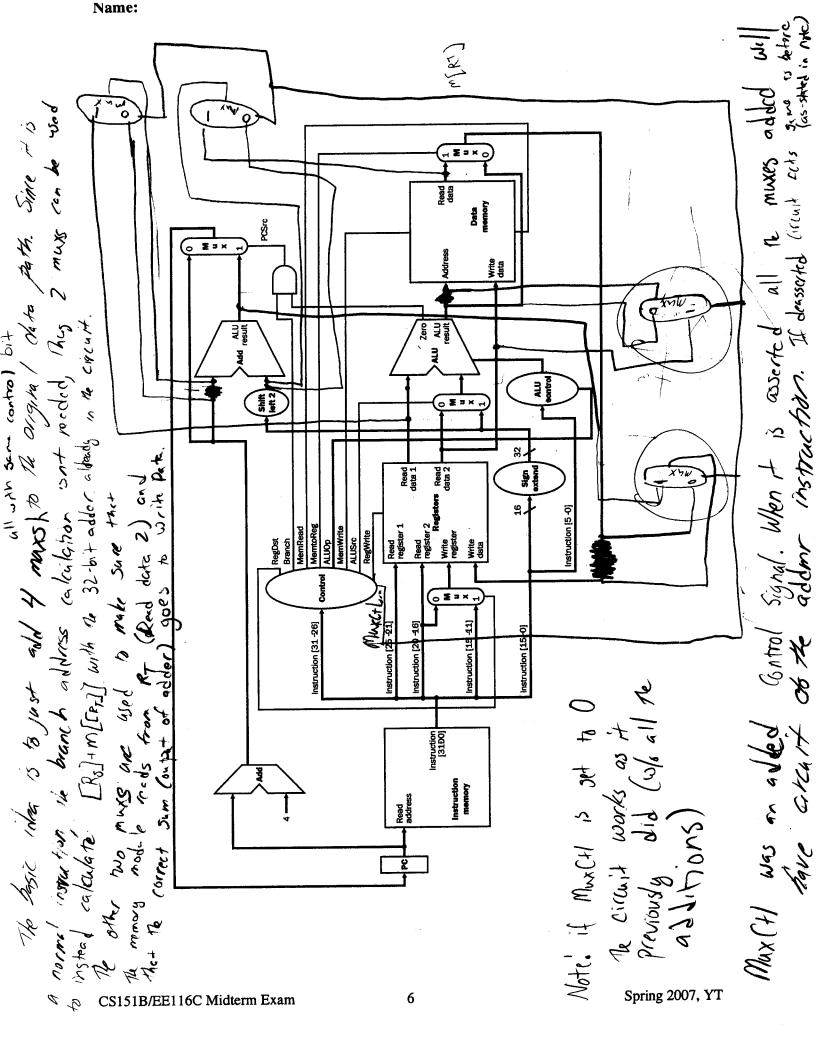

(6) Consider the single cycle MIPS implementation shown in Figure 5.17 (page 307) and Figure 5.18 (page 308).

27/33

Your task is to modify this implementation so that it supports a new instruction, addmr (add memory to register). The format of the instruction is the same as R-Format instructions. However, the least significant 11 bits (funct and shamt) are unused. The opcode of the new instruction is 110100. The function performed by this instruction is:

$$R_d \leftarrow [R_s] + M[[R_t]]$$

The instruction stores in the  $R_d$  register the sum of the  $R_s$  register and a 32-bit word from memory from the address specified by the  $R_t$  register. You can assume that the value in the  $R_t$  register is a multiple of 4.

When coming up with you modified design, you must take into account the cost of any additional hardware. Specifically, the costs of possible new hardware components are ordered as follows:

Thus, a gate is cheaper than a MUX which is cheaper than a flip-flop, etc. Each "cheaper than" means cheaper by a factor of 2.

The existing instructions, listed in Figure 5.18, must continue to function correctly. The new addmr instruction as well as the existing instructions must execute in a single cycle. You cannot modify and of the modules in the datapath. However, if necessary, you can add new modules.

Your top priority is a low-cost design. Your second priority is to minimize the changes to the datapath.

Note: if you need to add any new building blocks to the datapath or the control, it is **your responsibility** to make sure that it is completely clear **exactly** how each wire is connected to the new building block. If the new building block is not a copy of an already existing building block, you **must** draw the implementation of the new building block. (You do not have to show the implementation of standard MUXes). Make sure that your drawings are not messy.

- A) Explain the basic idea of your modifications in 2-4 clear sentences.

- B) Show the necessary modifications to the datapath. For your convenience, a copy of the datapath is on the next page and you <u>must</u> use it (together with other drawings, as you wish) to show your modifications.

- C) Are any new control signals required? If so, list them with an explanation and identify them on the datapath diagram.

- D) Modify Figure 5.18 as necessary for the new instruction. If you add any new control signals, be sure to include them and specify their values for <u>all</u> instructions. For your convenience, a copy of Figure 5.18 is on the page following the datapath. You <u>must</u> use it to show the modifications

Write your answer on the next two pages.

**Figure 5.18:**

| Instru-<br>ction | Reg-<br>Dst | i . | Memto-<br>Reg | Reg<br>Write | Mem<br>Read | Mem<br>Write | Branch | ALUOp1 | ALUOp0 | Monstart |   |   |

|------------------|-------------|-----|---------------|--------------|-------------|--------------|--------|--------|--------|----------|---|---|

| R-format         | 1           | 0   | 0             | 1            | 0           | 0            | 0      | 1      | 0      | 0        |   |   |

| lw               | 0           | 1   | 1             | 1            | 1           | 0            | 0      | 0      | 0      | 0        |   |   |

| sw               | Х           | 1   | х             | 0            | 0           | 1            | 0      | 0      | 0      | 0        |   | ! |

| beq              | Х           | 0   | х             | 0            | 0           | 0            | 1      | 0      | 1      | 0        |   |   |

| addmr            | 1           | X   | X             | 1            | 1           | 0            | 0      | X      | Χ      |          | · |   |

Note: my implementation doesn't use ALU module