BERKELEY · DAVIS · IRVINE · LOS ANGELES · RIVERSIDE · SAN DIEGO · SAN FRANCISCO SANTA BARBARA · SANTA CRUZ

## CS M151B / EE M116C Final Exam

All work and answers should be written directly on these pages, use the backs of pages if needed.

This is an open book, open notes final – but you cannot share books, notes, or calculators.

We strictly follow UCLA's policy on academic dishonesty – keep your eyes on your own paper.

| NAME:                    | NAME: Solutions                 |  |                 |           |               |  |

|--------------------------|---------------------------------|--|-----------------|-----------|---------------|--|

| ID:                      |                                 |  |                 | Use Darge | <u>n</u> 9498 |  |

| Problem 1 (15 points): _ |                                 |  | the same though |           | the stage     |  |

| Problem 2 (15 points): _ | to or applications with lots of |  |                 |           |               |  |

| Problem 3 (20 points): _ |                                 |  |                 |           |               |  |

| Problem 4 (10 points): _ | All Degling                     |  |                 |           |               |  |

| Problem 5 (20 points): _ | and a black of the second       |  |                 |           |               |  |

| Problem 6 (20 points): _ |                                 |  |                 |           |               |  |

| Total:                   | (out of 100 points)             |  |                 |           |               |  |

| Problem 7 (OPTIONAL      | ):                              |  |                 |           |               |  |

|                          |                                 |  |                 |           |               |  |

| 1. | statem<br>term, j | ing a Blank? (15 points): Given the following statements, fill in the blanks with the terms below the ent. You may reuse terms in case the statement has multiple blanks. Rather than writing the entire ust use the letter preceding the term to fill in the blank.  Ideally, the CPI for a single-issue (i.e. scalar) 5-stage pipeline would approach |

|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                   | A. 1.0 B. 0.5 C. 5.0 D. 0.25 E. 2.5                                                                                                                                                                                                                                                                                                                     |

|    | b.                | A 5-stage pipeline that is initially empty would reach steady state in the cycle, assuming it                                                                                                                                                                                                                                                           |

|    |                   | does not encounter any hazards.                                                                                                                                                                                                                                                                                                                         |

|    |                   | A. 1st B. 2nd C. 3rd D. 4th E. 5th                                                                                                                                                                                                                                                                                                                      |

|    | c.                | For a particular application, you try two different processors - Alpha and Beta. These processors                                                                                                                                                                                                                                                       |

|    |                   | Alpha and Beta are identical except that Alpha's L1 data cache has double the block size of Beta's L1                                                                                                                                                                                                                                                   |

|    |                   | data cache, but half the associativity. Their total size is the same though. You would think that Alpha would do better on applications with lots of $\underline{\mathcal{B}}$ and Beta would do better on applications                                                                                                                                 |

|    |                   | with lots of $\underline{E}$ .                                                                                                                                                                                                                                                                                                                          |

|    |                   | <ul> <li>A. Temporal locality</li> <li>B. Spatial locality</li> <li>C. Cold misses</li> <li>D. Capacity misses</li> <li>E. Conflict misses</li> <li>F. Instruction-level parallelism</li> </ul>                                                                                                                                                         |

|    | d.                | If your application mainly has stores that write an address once and have poor spatial and temporal locality, then you should use a cache.                                                                                                                                                                                                              |

|    |                   | <ul> <li>A. Write through, write allocate</li> <li>B. Write through, write around</li> <li>C. Writeback, write allocate</li> <li>D. Writeback, write around</li> </ul>                                                                                                                                                                                  |

| e. | Virtual memory provides A, B. Choose all answers that apply.                                                                                                                                                                                            |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | <ul> <li>A. Protection between applications</li> <li>B. A larger memory space</li> <li>C. Lower load latency</li> <li>D. Fewer register spills</li> </ul>                                                                                               |

| f. | Your 5-stage pipelined architecture (with a 3 cycle branch penalty) currently uses hardware-based stalling to deal with control hazards. If you were to use dynamic branch prediction (i.e. a table of 2-bit                                            |

|    | predictors) you would expect that CPI would likely, cycle time could possibly, and                                                                                                                                                                      |

|    | the instruction count would                                                                                                                                                                                                                             |

|    | <ul><li>A. increase</li><li>B. decrease</li><li>C. stay the same</li></ul>                                                                                                                                                                              |

| g  | Your 5-stage pipelined architecture currently resolves data hazards with hardware-based stalling – no forwarding logic. If you were to use NOP insertion instead, you would expect that CPI would likely, cycle time could possibly                     |

|    | <ul> <li>A. increase</li> <li>B. decrease</li> <li>C. stay the same</li> </ul>                                                                                                                                                                          |

| ł  | Simultaneous multithreading (also known as hyperthreading) may help improve but can reduce                                                                                                                                                              |

|    | <ul> <li>A. ALU latency</li> <li>B. Processor utilization (i.e. throughput)</li> <li>C. Single thread performance (when run with other threads)</li> <li>D. L1 cache latency</li> </ul>                                                                 |

| i  | . Direct Memory Access (DMA) means                                                                                                                                                                                                                      |

|    | A. that the processor can directly access memory instead of going through the TLB or page table B. that the processor makes a translation from virtual to physical address, and then directly accesses memory without going through the cache hierarchy |

|    | C. that I/O devices can directly read/write memory without processor intervention D. that cache can directly access DRAM without address translation                                                                                                    |

|    | De mini vivaire viva di la company                                                                                                                                                                                                                      |

2. *Hazard Countin'* (15 points): Assume you are using the 5-stage pipelined MIPS processor, with a two-cycle branch penalty. In the following code:

We will measure the number of cycles to execute this code starting with the first lw instruction entering the pipeline (assume it is not stalled by any hazards) and continuing until the sw at the bottom leaves the pipeline. The bne at the bottom is taken 100 times. The beq is taken 50 times. Assume that all memory is ideal – i.e. we have no cache misses to worry about. Further assume that these 11 instructions are stored contiguously in memory.

a. Suppose we do not have any data forwarding hardware – we stall on data hazards. The register file is still written in the first half of a cycle and read in the second half of a cycle, so there is no hazard from WB to ID. We handle branch hazards with a branch predictor that always guesses branch not taken. But this is *only for conditional branches* – jumps are handled differently and do not cause branch hazards. Calculate the number of cycles that this sequence of instructions would take, and show your work.

Total cycles:\_\_\_\_\_

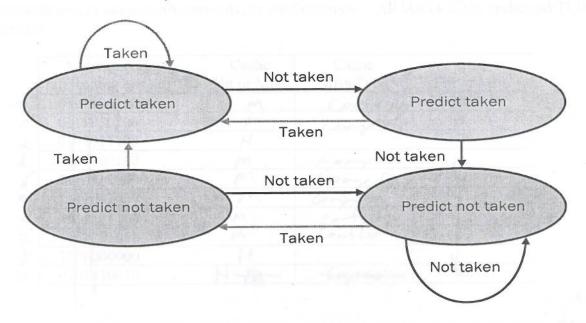

b. Now assume we have full data forwarding as covered in class, and we have an 8 entry, 2-bit branch predictor with FSM as shown below. Assume that we use the simplified branch indexing formula: index = (PC>>2) % predictor\_size. The symbol % represents the modulo operator. Further assume that all entries in the branch predictor start in the state at the upper left of the FSM. But this predictor is only used for conditional branches – jumps are handled differently and do not cause branch hazards. Calculate the number of cycles that this sequence of instructions would take, and show your work.

Total cycles:\_\_\_\_

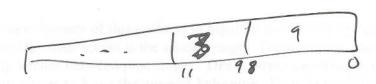

- 3. Cache Me If You Can (20 points): Find the cache hit or miss stats for a given set of addresses. The data cache we will evaluate is a 256B, direct mapped cache with 64-byte blocks. You are using a 48-bit virtual address space, a 32-bit physical address space, and use 512B pages in your virtual memory. Your TLB has 32 entries (i.e. locations to store translations) and is 4-way associative. Each entry in the page table has one extra bit beyond the physical page number.

- a. Find the hit/miss behavior of the data cache and TLB for the given byte address stream, and label cache misses as compulsory, capacity, or conflict misses. All blocks in the cache and TLB are initially invalid.

|   | Address in Binary          | Cache       | Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TLB         |

|---|----------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|   | (all leading bits are 0's) | Hit or Miss | Miss Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Hit or Miss |

| λ | 0101100110                 | M           | (Dompolo)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | M           |

| • | 0111010100                 | m           | como u/so                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | H           |

|   | 0101011100                 | Н           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Н           |

|   | 1000100110                 | m.          | Conjuls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | M.          |

| 1 | 1110111000                 | M           | Compalo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14          |

|   | 1111011000                 | m           | Congulso                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VI          |

|   | 0111101100                 | M           | Conflict                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| _ | 1111101010                 | m           | Conflict                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| 2 | 1000000000                 | 1+          | Contract of the last of the la | N/          |

| 1 | 0101110010                 | H-MA        | Capait                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V           |

- b. What percent of the pages in virtual memory can fit in physical memory at one time?  $\frac{2^{3}}{2^{3}} = \frac{100}{2}$

- c. How large (in bytes) is the page table?  $2^{37} + 38$

- d. What fraction of the total number of page translations can fit in the TLB?  $\frac{2}{2^{39}} = \frac{1}{2^{37}}$

- e. What bits of a virtual address will be used for the index to the TLB? Specify this as a range of bits i.e. bits 4 to 28 will be used as the index. The least significant bit is labeled 0 and the most significant bit is labeled 31.

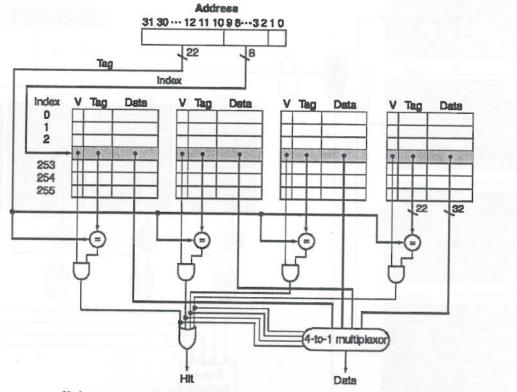

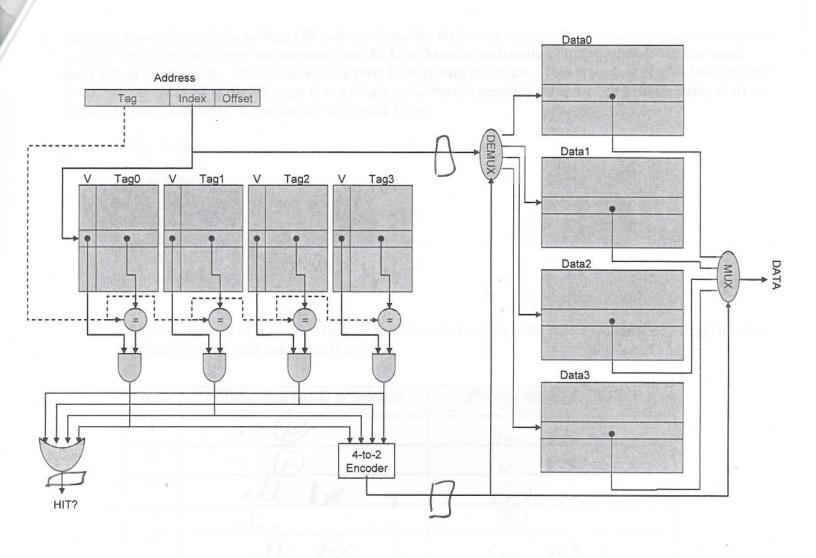

4. Serial (Access) Killer (10 points): Consider the 4-way set associative cache we explored in class:

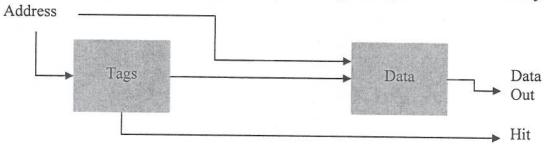

This is known as a *parallel access* cache because the Tag and Data components are accessed in parallel. Another way to design a cache is to put the components in series – a *serial access* cache. This type of cache can be more power efficient, but has longer latency. At a high level, a serial access cache just looks like this:

The address is used to index the tag and data components of the cache, but only one way of the data component is actually driven out (instead of all ways in the parallel access cache). The two outputs are still the same (Hit and the Data Out).

One way to deal with the longer latency of this cache is to pipeline it over two cycles. The tag access is the first stage of the pipeline, and the data access is the second stage. The next page has the serial access design in more detail, but it is missing latches between pipe stages. **Draw boxes on wires to indicate where values should be saved in between cycles to have the correct behavior.** Keep in mind that we want to have two accesses to the cache in the pipeline at the same time (don't worry about hazards). For timing purposes, we will keep the 4-to-2 encoder, AND, and OR gates in the first stage of the pipeline, and the demultiplexor (DEMUX) in the second stage of the pipeline. Don't worry about the address offset.

5. Starting Some Static (Scheduling) (20 points): Consider the 2-way superscalar processor we covered in class – a five stage pipeline where we can issue one ALU or branch instruction along with one load or store instruction every cycle. This processor has data forwarding hardware. This processor is a VLIW machine. Branches are resolved in the ID stage (i.e. a single cycle branch penalty) – and we use branch delay slots to avoid any branch hazards. Consider the following loop:

Loop: lw \$t1, 0 (\$s0)

lw \$t2, 4 (\$s0)

addu \$t2, \$t1, \$t2

lw \$t3, 0 (\$t2)

add \$s2, \$s2, \$t3

addi \$t0, \$t0, 1

addi \$s0, \$s0, -8

bne \$t0, \$s1, Loop

a. First you will need to schedule (i.e. reorder) the code (use the table below) to reduce the total number of cycles required (but don't unroll it...yet).

| Cycle | 1 <sup>st</sup> Issue Slot (ALU or Branch) | 2 <sup>nd</sup> Issue Slot (LW or SW) |

|-------|--------------------------------------------|---------------------------------------|

| 1     |                                            | Iw Stl a                              |

| 2     | $\sim$                                     | 1w \$125                              |

| 3     | all: # 50                                  |                                       |

| 4     | alla                                       | @                                     |

| 5     | all: It &                                  | lw #+3 d                              |

| 6     | bne                                        | 0                                     |

| 7     | all e                                      | (N)                                   |

| 8     |                                            |                                       |

| 9     |                                            |                                       |

| 10    |                                            |                                       |

| 11    |                                            |                                       |

| 12    |                                            |                                       |

| 13    |                                            |                                       |

(this is the same loop as the page before – just replicated for your convenience)

Loop: A lw \$t1, 0 (\$s0)

Loop: A lw \$t2, 4 (\$s0)

Laddu \$t2, \$t1, \$t2

Allw \$t3, 0 (\$t2)

Laddi \$s2, \$s2, \$t3

Laddi \$t0, \$t0, 1

Laddi \$s0, \$s0, -8

Loop to be supported to the support of the supported to the support of the suppor

b. Second, unroll the loop once (i.e. so the loop body contains two iterations) and schedule (i.e. reorder) the code (use the table below) to reduce the total number of cycles required.

| Cycle | 1 <sup>st</sup> Issue Slot (ALU or Branch) | 2 <sup>nd</sup> Issue Slot (LW or SW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | (~)                                        | al /w #+1,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2     |                                            | 161 lu #+2, 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3     | add: \$to                                  | al In \$14, -8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4     | c) all \$+2                                | 1 bz &w 115, -4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5     | a) all: \$50                               | 12 d1 14 \$+3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6     | Ex alla \$15                               | The state of the s |

| 7     | s) all                                     | 12 lw #16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8     | bae                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9     | er add                                     | (N)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10    | a ver cultur benneh hugands. Candi         | reput branches and the state of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11    | m. To nandio data he are a we use          | dual ferwarding, militaries in strad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12    | rem in the next instruction is deper       | den an the load to Alfaed Light at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 13    | are and the fund institutions later (to    | h the next texture in 16 piles at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

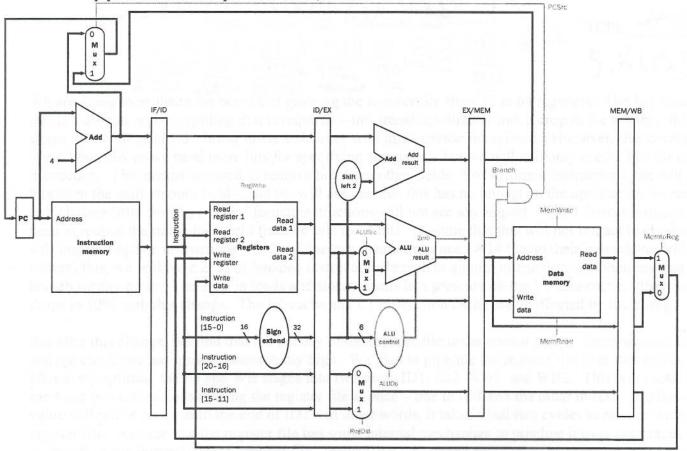

6. You'll be looking FORWARD to these HAZARDS just being a distant MEMORY ... (20 points): Consider the scalar pipeline we have explored in class, shown below.

For the rest of this question, this architecture will serve as the baseline that we will compare against. It has a 2 GHz clock, and the application that we are testing on this architecture executes 10 billion instructions. Branches are resolved in the MEM stage as shown in the figure above. To handle branch hazards, we will always predict that conditional branches will not be taken. Assume that we have some way of dealing with jumps so that they never cause branch hazards. Conditional branches (beq and bne) are taken 30% of the time with this application. To handle data hazards, we use data forwarding, just as we covered in class, stalling for one cycle when a load is followed by a dependent instruction. 25% of loads are immediately followed by a dependent instruction (i.e. the next instruction is dependent on the load). 10% of loads are followed by a dependent instruction exactly two instructions later (i.e. the next instruction is independent of the load, but the instruction after that is dependent on the load). And 5% of loads are followed by a dependent instruction exactly three instructions later. 25% of instructions are R-type, 30% are loads, 20% are bne or beg, 10% are jumps, and 15% are stores. We are using a 16KB direct mapped instruction cache with 32 byte blocks that has a miss rate of 10% for this application. Our data cache is a 32KB 4-way set associative cache with 64 byte blocks and a miss rate of 15%. And we have a unified L2 cache that is a 1MB 8-way set associative cache with 128 byte blocks and a miss rate of 5%. The L1 caches can be accessed in a single cycle, and the miss penalty to go to the L2 is 20 cycles from both L1 caches. The L2 has a 150 cycle miss penalty. Assume that stores may stall the pipeline – and should be considered in MCPI.

a. Find the TCPI for this architecture and application. Show your work below:

BCPI = 1.0+ (.3) × (.25) (1) + (.2) (.3) (.3) (.3) (.3) (.3) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45) (.45

We are going to evaluate the benefit of growing the register file from 32 to 64 registers. The key benefit from this is a drop in register spilling that is required – this translates directly into a drop in the number of loads and stores. We will need 1/3<sup>rd</sup> fewer loads and stores with this increase in registers. However, this change will impact our ISA as we need more bits for specifying a register – but we will still only use 32 bits for each instruction. This means we need to remove bits from other fields. For R format instructions, we will take the bits from the shift amount field – and we will assume that this has no impact on the application we are using (which does little shifting). The J format instructions will not see any impact. The I format instructions will need to reduce the immediate field from 16 bits to 14 bits. Assume that this will not impact loads/stores, but it will impact beq/bne instructions – 25% of bne/beq instructions need > 14 bits in their immediate field. To address this, we will have 25% of bne/beq instructions branch to a jump instruction, and then use that jump to branch further away. The drop in loads and stores means less pressure on the L1 data cache – the miss rate drops to 10% with this change. The L2 cache and L1 instruction cache are unaffected by the change.

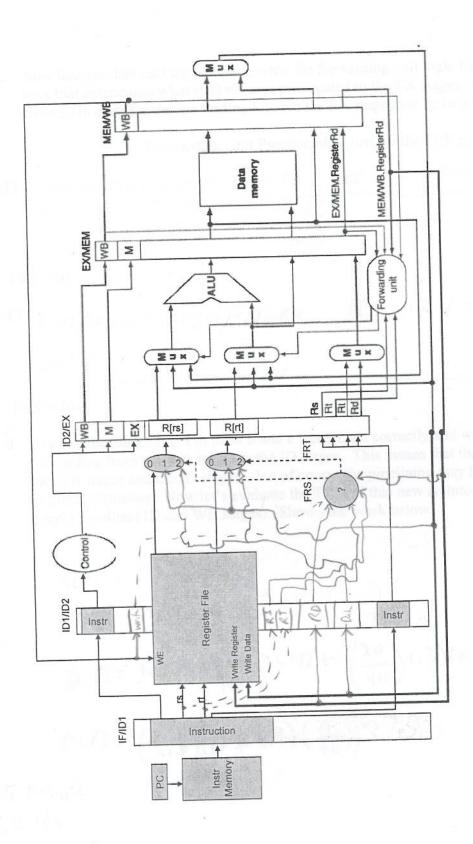

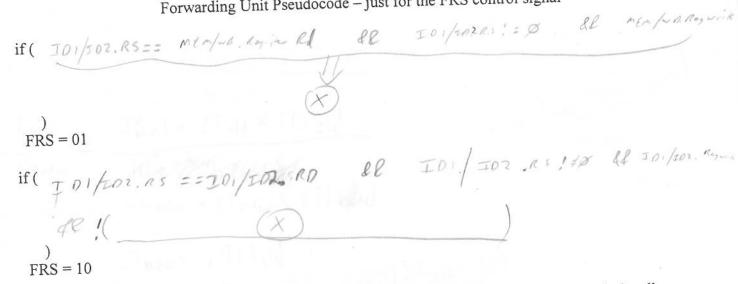

But after this change, we find that the latency of the register file is the critical path to determine our cycle time and the clock rate has grown unacceptably high. We plan to pipeline the register file over two cycles – effectively splitting the ID and WB stages into two each: ID1, ID2, WB1, and WB2. This will mean that we can have two instructions reading the register file at once – one in ID1 and the other in ID2. But the register value will not be ready until the end of ID2 – in other words, it takes a full two cycles to read or write the register file. Assume that the register file has some internal mechanism to pipeline it over two stages – don't worry about the internals of the register file. Instead, we will worry about what happens when we read and write the same register. Pipelining the register file over multiple cycles breaks our assumption that we can write to the register file at the first half of the cycle and read from the register file in the second half. Instead – we will have to add some additional forwarding hardware. At the ID2/EX latch, we will store one of three values for R[rs], and one of three values for R[rt]. The muxes in front of the latch show these three options – but two of these options for each mux are currently unconnected.