BERKELEY • DAVIS • IRVINE • LOS ANGELES • RIVERSIDE • SAN DIEGO • SAN FRANCISCO

## CS M151B / EE M116C Final Exam

Before you start, make sure you have all 13 pages attached to this cover sheet.

All work and answers should be written directly on these pages, use the backs of pages if needed.

This is an open book, open notes final – but you cannot share books, notes, or calculators.

| NAME:                   |

|-------------------------|

| ID:                     |

| blem 1 (10 points):     |

| blem 2 (10 points):     |

| blem 3 (10 points):     |

| blem 4 (10 points):     |

| blem 5 (20 points):     |

| blem 6 (10 points):     |

| blem 7 (30 points):     |

| al: (out of 100 points) |

1. I Amdahl-ighted with Tradeoffs (10 points): Given the following problems, suggest one solution and give one drawback of the solution. Be brief, but specific.

## **EXAMPLE**

Problem: long memory latencies

Solution: Caches

Drawback: when the cache misses, the latency becomes worse due to the cache access latency

We would not accept solutions like: "do not use memory", "use a slower CPU", "cache is hard to spell", etc

Problem: too many capacity misses in the data cache

Solution:

increase cache size

drawback:

slower cache access time

Problem: too many control hazards

Solution: Loop unrolling with compiler

drawback: Larger code size

Problem: our carry lookahead adder is too slow

Solution: Hierarchical CLA

drawback: more hardware

Problem: we want to be able to use a larger immediate field in the MIPS ISA

Solution:

Reduce # registers in ISA

drawback:

more register spilling

Problem: the execution time of our CPU with a single-cycle datapath is too high

Solution:

pipeline

drawback:

more hardware

| 2. | branch penalty. Fu | 10 points): Assume you are using the 5-stage pipelined MIPS processor, with a three-cycrther assume that we always use predict not taken. Consider the following instruction e bne is taken once, and then not taken once (so 7 instructions will be executed total): | <u>le</u> |

|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|    | Loop:              | lw \$t0.512(\$t0)<br>lw \$t1,64(\$t0)                                                                                                                                                                                                                                 |           |

|    |                    | bne \$s0, \$t1) Loop<br>sw \$s1, 128(\$t0)                                                                                                                                                                                                                            |           |

Assuming that the pipeline is empty before the first instruction:

a. Suppose we do not have any data forwarding hardware – we stall on data hazards. The register file is still written in the first half of a cycle and read in the second half of a cycle, so there is no hazard from WB to ID. Calculate the number of cycles that this sequence of instructions would take:

| LW IF ID EX M WB  LW IF OO ID EX M WB  bne IF OOID EX M WB  LW OODF ID EX M WB  LW TF OOID EX M WB |     | Щ | 2  | 3  | 4 | >  | 6  | 7  | 81 | 4  | 10 | 111 | 12 | 13 | 14 | 15 | 161 | 17 | 18 | 19 | 201 | 211 | 24  |

|----------------------------------------------------------------------------------------------------|-----|---|----|----|---|----|----|----|----|----|----|-----|----|----|----|----|-----|----|----|----|-----|-----|-----|

| bne IFOOIDEX M WB                                                                                  | lw  | 拉 | ID | EX | M | W  |    |    |    |    |    |     |    |    |    |    | -   |    |    | 1  |     |     |     |

| lw OODF ID BX M W3                                                                                 | lw  |   | T  | 0  | 0 | ID | EX | M  | WB |    |    |     |    |    |    |    |     |    |    | 1  |     |     |     |

| IN OODE ID BX W MB                                                                                 | bne | 一 |    | T  | Г | T  | 0  | 10 | ID | EX | M  | WB  |    |    |    |    |     |    |    |    |     |     |     |

| LW X O C O TO EX M WB                                                                              | lw  |   |    |    |   |    | Ť  |    | 10 | 0  | 0  | T   | ID | EX | M  | MB |     |    |    |    |     |     |     |

|                                                                                                    | lw  |   |    |    | 1 |    | +  | t  | 1  | +  | Ť  |     | Ti | 0  | 0  | 10 | X   | M  | WB |    |     |     |     |

| PNS DIDEX W MR                                                                                     | bne |   |    |    | T |    | T  | 1  | 1  |    |    |     | 1  | 1  |    | *  | 0   | 0  | ID | EX | M   | /WB |     |

| SW IFIDEX M                                                                                        |     |   |    | 1  |   |    |    |    |    |    |    | 1   | 1  |    | 1  |    |     | 1  | IF | IC | E   | IM  | 8w) |

b. How many cycles would this sequence of instructions take with data forwarding hardware:

| 7   | 35.       | £. | -  | 1    | 0 | $\vdash$ | 0 | +        | -   |     | 1        | 4        | 1        | +      | 1       | 17)  |

|-----|-----------|----|----|------|---|----------|---|----------|-----|-----|----------|----------|----------|--------|---------|------|

| 1   | 10        | W  | M  | TAUS |   |          |   | $\vdash$ | _   |     | $\vdash$ | $\dashv$ | $\dashv$ | +      | 十       | -    |

|     | II        | 0  | D  | EX   | M | WB       |   |          |     |     |          |          | _        | 1      | 1       |      |

| 1   | 1         | 0  | 10 | 10   | 0 | DEX      | M | WB       |     |     |          |          |          |        | $\perp$ |      |

| 1   | $\dagger$ | 19 |    |      | 0 | 10       | 0 | 平        | M   | EX  | MI       | WB       |          |        |         | 9101 |

| 150 |           | 1  | +  | Lin  |   | 100      | 1 | ile      | 1£  | 0   | TIDI     | TEX      | M        | PINE   | 171     | i ai |

| 1   | 1         | 1  | 1  | +    | 1 | 1        |   | 111      | l h | 000 | 11       | 10       | IT       | XI THE | IM      | lw1  |

3. More \$ More Problems (10 points): Find the data cache hit or miss stats for a given set of addresses. The data cache is a 1KB, direct mapped cache with 64-byte blocks. Find the hit/miss behavior of the cache for a given byte address stream, and label misses as compulsory, capacity, or conflict misses. All blocks in the cache are initially invalid.

64-byte blk = 7 6 bit cache HK 1KB DM &= 7 210 effset  $\frac{2^{10}}{3^6} = 2^4 \Rightarrow 4 \text{ bit index}$ For 16 entries

| Address in Binary | Cache Hit or Miss | Cache<br>Miss Type |

|-------------------|-------------------|--------------------|

| 0011011010000     | M                 | Compulsory         |

| 0001011100000     | M                 | Compulsorx         |

| 0000011010000     | M                 | Compulsory         |

| 0011011100000     | M                 | Conflict           |

| 0011011010000     |                   | GV det falovo      |

| 0001011100000     | M                 | Conflict           |

| 0000011010000     | arran Hassis,     | spitansii ma       |

| 0011011100000     | M                 | Conflict           |

4. The Trouble with TLBs (10 points): Consider an architecture with 32-bit virtual addresses and 1 GB of physical memory. Pages are 32KB and we have a TLB with 64 sets that is 8-way set associative. The data and instruction caches are 8KB with 16B block sizes and are direct mapped – and they are both virtually indexed and physically tagged. Assume that every page mapping (in the TLB or page table) requires 1 extra bit for storing protection information. Answer the following:

a. How many pages of virtual memory can fit in physical memory at a time?

1618 phy min =7  $2^{30}$   $2^{30}/2^{15} = 2^{15}$ 32KB page size => 215

b. How large (in bytes) is the page table? 218 by tes

entry size = phy page num = 1561ts, but assume lextra bit for protection = 716 bits = 2bytes

#entries = # virtual pages = 237/218 = 217 page table size = 2×217 = 216

c. What fraction of the total number of page translations can fit in the TLB? 1/256

64 sets=> 26 8 ways => 23

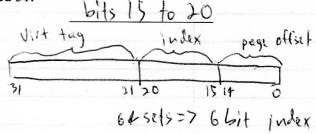

d. What bits of a virtual address will be used for the index to the TLB? Specify this as a range of bits – i.e. bits 4 to 28 will be used as the index. The least significant bit is labeled 0 and the most significant bit is labeled 31.

5. Starting Some Static (Scheduling) (20 points): Consider the 2-way superscalar processor we covered in class – a five stage pipeline where we can issue one ALU or branch instruction along with one load or store instruction every cycle. Suppose that the branch delay penalty is two cycles and that we handle control hazards with branch delay slots (since the penalty is two cycles, and this is a 2-way superscalar processor, that would be four instructions that we need to place in delay slots). This processor has full forwarding hardware. This processor is a VLIW machine. How long would the following code take to execute on this processor assuming the loop is executed 200 times? Assume the pipeline is initially empty and give the time taken up until the completed execution of the instruction sequence shown here. First you will need to schedule (i.e. reorder) the code (use the table below) to reduce the total number of cycles required (but don't unroll it...yet).

| Total # of cycles for 200 iterations: | 1200 |  |

|---------------------------------------|------|--|

(Hint – schedule the code first for one iteration, then figure out how long it will take the processor to run 200 iterations of this scheduled code)

Loop:

lw \$t0, 0 (\$s0) lw \$t1, 0 (\$t0) add \$t1), \$s1, \$t1

sw \$1) 0 (\$t0) # you may assume that this store never goes to the same address as the first load addi \$50, \$50, 4

bne(\$\$0,)\$\$2, Loop

| Cycle | 1 <sup>st</sup> Issue Slot (ALU or Branch)                                                      | 2 <sup>nd</sup> Issue Slot (LW or SW)  |

|-------|-------------------------------------------------------------------------------------------------|----------------------------------------|

| 1     | add; \$50, \$50,4                                                                               | lw \$40,0(\$50)                        |

| 2     | Constate recessor factored at                                                                   | in the Younger leutily to every your   |

| 3     |                                                                                                 | lw \$1,0(\$60)                         |

| 4 ~   | bne \$50, \$52, Loop                                                                            | Talder agent server (extinding) missi  |

| 5     | add \$1,\$51,\$t1                                                                               | NOP                                    |

| 6     | NOP                                                                                             | sw \$t1,0(\$t0)                        |

| 7     | 37                                                                                              | a transfer of the same                 |

| 8     | <mark>aga vilosõ</mark> je (1813) sait el võtsa 560 ki<br>Mark kaistiel ja tid verdiinen kanlad | E relationed to be so will be at a re- |

| 9     |                                                                                                 | le beledet i i i i i i i               |

| 10    | 4. 47                                                                                           |                                        |

| 11    |                                                                                                 |                                        |

| 12    |                                                                                                 | But he                                 |

| 13    | La vala del d                                                                                   | (Kalisa aa                             |

sub 4 since addi moved ahead

| Cycle | 1 <sup>st</sup> Issue Slot (ALU or Branch) | 2 <sup>nd</sup> Issue Slot (LW or SW)    |

|-------|--------------------------------------------|------------------------------------------|

| 1     | addi \$50, \$50,4                          | lw \$40, 0 (\$50)                        |

| 2     | , , , , , , , , , , , , , , , , , , , ,    | lw 6+2,0(850)                            |

| 3     |                                            | lw \$41, 0 (\$40)                        |

| 4     |                                            | lw \$43, 0 (\$42)                        |

| 5     | add \$1,\$51,\$t1                          |                                          |

| 6     | bne \$50, \$52, Loop                       | sw \$t1, 0 (\$t0)                        |

| 7     | add \$t3, \$41, \$t3                       | NOP                                      |

| 8     | NOP                                        | sw \$t3, 0(\$t2)                         |

| 9     | n mess (                                   |                                          |

| 10    | no Astronomical Control                    | 4507 (970)678                            |

| 11    |                                            |                                          |

| 12    |                                            | 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 |

13

Evaluate the performance of this prediction scheme on the following sequence of PCs. The table shows the address of the branch and the actual direction of the branch (taken or not taken). You get to fill in whether or not the branch predictor would guess correctly or not. Each node of the FSM is marked with the 2-bit value representing that state. Assume that all predictors are initialized to 00. To find an index into a predictor, assume we use the simplified branch indexing formula: index = PC % predictor\_size. The symbol % represents the modulo operator. Predictor\_size will be different according to the predictor.

| PC   | Actual Direction | Correctly Predicted?         |

|------|------------------|------------------------------|

| 128  | T                | 13.5 mm                      |

| 640  | NT               | 2017 method                  |

| 1152 | NT               | and the second second        |

| 128  | /T               |                              |

| 640  | T                | and the second second        |

| 1152 | NT               |                              |

| 128  | T                | and the second second        |

| 640  | NT               |                              |

| 1152 | NT               |                              |

| 128  | T                |                              |

| 640  | T                | and the second second second |

| 1152 | NT               |                              |

|      | 1024  |               |      |            | 512   |               |      |            | 768   |               |      |            |                  |                      |

|------|-------|---------------|------|------------|-------|---------------|------|------------|-------|---------------|------|------------|------------------|----------------------|

| PC   | index | current state | pred | next state | index | current state | pred | next state | index | current state | pred | next state | actual direction | Correctly predicted? |

| 128  | 128   | 00            | NT   | 01         | 128   | 00            | NT   | 01         | 128   | 00            | NT   | 01         | Т                | N                    |

| 640  | 640   | 00            | NT   | 00         | 128   | 01            | NT   | 00         | 640   | 00            | NT   | 00         | NT               | Υ                    |

| 1152 | 128   | 01            | NT   | 00         | 128   | 00            | NT   | 00         | 384   | 00            | NT   | 00         | NT               | Υ                    |

| 128  | 128   | 00            | NT   | 01         | 128   | 00            | NT   | 01         | 128   | 01            | NT   | 11         | Т                | N                    |

| 640  | 640   | 00            | NT   | 01         | 128   | 01            | NT   | 11         | 640   | 00            | NT   | 01         | Т                | N                    |

| 1152 | 128   | 01            | NT   | 00         | 128   | 11            | T    | 10         | 384   | 00            | NT   | 00         | NT               | Υ                    |

| 128  | 128   | 00            | NT   | 01         | 128   | 10            | Т    | 11         | 128   | 11            | Т    | 11         | Т                | Υ                    |

| 640  | 640   | 01            | NT   | 00         | 128   | 11            | Т    | 10         | 640   | 01            | NT   | 00         | NT               | Υ                    |

| 1152 | 128   | 01            | NT   | 00         | 128   | 10            | T    | 00         | 384   | 00            | NT   | 00         | NT               | Υ                    |

| 128  | 128   | 00            | NT   | 01         | 128   | 00            | NT   | 01         | 128   | 11            | T    | 11         | Т                | N                    |

| 640  | 640   | 00            | NT   | 01         | 128   | 01            | NT   | 11         | 640   | 00            | NT   | 01         | Т                | N                    |

| 1152 | 128   | 01            | NT   | 00         | 128   | 11            | T    | 10         | 384   | 00            | NT   | 00         | NT               | Υ                    |

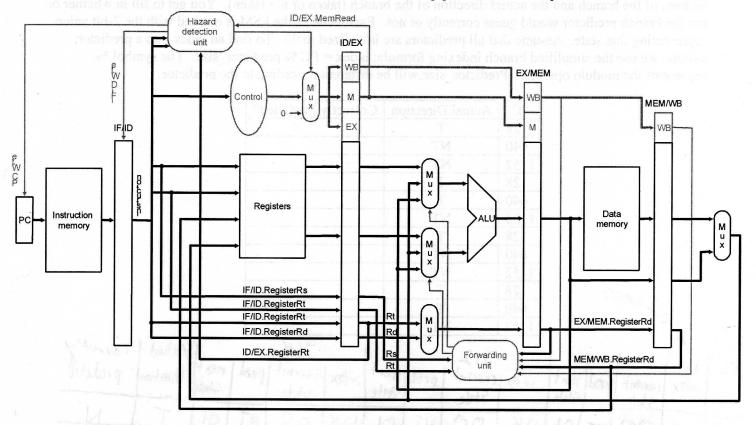

7. With Friends Like These... (30 points): Consider the scalar pipeline we have explored in class:

a. (10 points) Suppose 10% of instructions are stores, 15% are branches, 25% are loads, and the rest are R-type. 30% of all loads are followed by a dependent instruction. We have full forwarding hardware on this architecture. We use a predict not taken branch prediction policy and there is a 2 cycle branch penalty. This means that the PC is updated at the end of the EX stage – after the comparison is made in the ALU. One third of all branches are taken. There is an instruction cache with a single cycle latency and a miss rate of 10% and a data cache with a single cycle latency and a miss rate of 20%. We have an L2 cache that misses 5% – it has a 10 cycle latency – and memory has a 100 cycle latency. Find the TCPI for this architecture.

$$TCPI = 3.725$$

$$TCPI = BCPI + MCPI = 1.175 + 2.55$$

$$BCPI = 1 + 0.3 \times 0.25 \times 1 + \frac{1}{3} \times 0.15 \times 2 = 1.175$$

$$Iw depend br penalty$$

$$MCPI = 0.1 \times (10 + 0.05 \times 100) + (0.1 + 0.25) \times 0.2 \times (10 + 0.05 \times 100)$$

$$Iwst misses$$

$$= 2.55$$

b. (5 points) Your friend has a flash of brilliance – "I know a way to get rid of stalls in this pipeline. The reason we have to stall now is because a load can have a dependent instruction follow it through the pipeline, and we cannot forward the load's data until the end of the MEM stage – but the dependent instruction needs it at the beginning of the EX stage. So what if we add another ALU that recomputes what we did in EX if the instruction before it is a load and it is dependent on the load?" This ALU will be in the memory stage of the pipeline as shown below in this simplified picture:

Is your friend right or wrong? If they are wrong, give an example of when we would still need to stall.

They are right:

Or

Counter example: Lw +> Lw deflending will still (auge bubble. Lw needs all 5 stages. Result of EX is used as input address of DM.

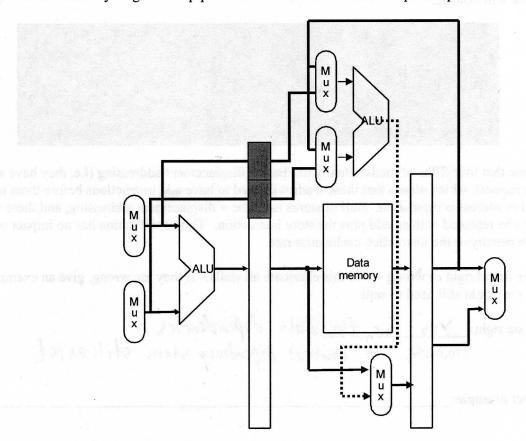

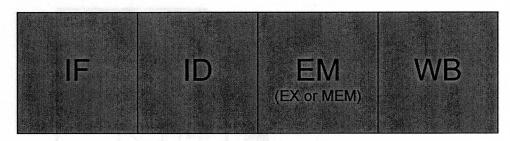

c. (5 points) Another friend offers an alternative – using the original pipeline from part a, let's get rid of base + displacement addressing for loads and stores. Loads and stores can only use register addressing now. This will allow us to combine EX and MEM into one stage (called EM) and avoid the need to stall entirely. Instructions will either use the ALU or memory – but not both. There is still forwarding hardware, but now we only need to forward from the EM/WB latch to the EM stage ALU. The pipeline will now be:

Suppose that four fifths of loads actually use base + displacement addressing (i.e. they have a non-zero displacement), which means that these loads will need to have add instructions before them to do their effective address computation. Half of stores use base + displacement addressing, and these will also need to be replaced with an add plus the store instruction. This modification has no impact on the branch penalty or the instruction cache miss rate.

Is your friend right or wrong – will this eliminate all stalls? If they are wrong, give an example of when we would still need to stall.

| They are right: | yes.     | for 7 | he date | a dependen | reies, | 9.           |  |

|-----------------|----------|-------|---------|------------|--------|--------------|--|

| Or              | However, | the   | control | dependency | stalls | still exist. |  |

| Counter examp   | ole:     |       |         |            |        |              |  |

d. (10 points) A third friend has a different idea (it may be time for you to get new friends who don't talk about architecture all the time). Forget about trying to eliminate hazards – she says we should just use superpipelining and get a win on cycle time. Take the original architecture from part a – ignore the suggestions from b and c – and assume that the stages have the following latencies:

| Stage | Latency (in picoseconds) |

|-------|--------------------------|

| IF    | 200                      |

| ID    | 100                      |

| EX    | 200                      |

| MEM   | 200                      |

| WB    | 100                      |

Your friend suggests a way to cut the IF, EX, and MEM stages in half – just increase the pipeline depth and make each of these stages into two stages. So your pipeline would now have IF1, IF2, ID, EX1, EX2, MEM1, MEM2, and WB stages – each of which would have 100 picosecond latency. Your friend also finds a way to do full forwarding between stages - even in the ALU - but loads are still a problem. In fact, load stalls will increase now because of this increase in pipeline depth. To help you figure out the new # of pipeline stalls from load data hazards, use the following table:

|     |    | TH 172 ID EX 1 EX 2 MI M2 WB  IFI 172 ID O O O EN EX 2 |     |     |          |      |           |       | 1110 1 |

|-----|----|--------------------------------------------------------|-----|-----|----------|------|-----------|-------|--------|

| . , | 1  | 2                                                      | 5   | 4   | 1        | 16   | 17        | 18    | 19     |

| Lw  | AT | IP2                                                    | ID  | EXI | EX)      | MI   | 192       | WB    |        |

|     |    | 1EI                                                    | 1/2 | ID  | 0        | 0    | 0         | Al    | EY2    |

| beg | IH | 165                                                    | ID  | EXI | EXZ<br>O | 五五   | M2<br>TF2 | WB ID | ENI    |

|     | 1  | ١                                                      | A   | i   | ( '      |      |           |       |        |

|     |    |                                                        | 1   |     |          | i.e. | ,         |       |        |

|     |    | br                                                     | P   | enü | Ty       | =    | 4         |       |        |

have dependents 1 cycle later.

| •   | % of Loads | Distance of the next dependent instruction |       |          |

|-----|------------|--------------------------------------------|-------|----------|

| 100 | 30%        | 1 cycle                                    |       | 3 cycles |

|     | 20%        | Exactly 2 cycles later                     | stall | 2 cycles |

| 35  | 20%        | Exactly 3 cycles later                     | stall | 1 cycle  |

|     | 10%        | Exactly 4 cycles later                     |       |          |

|     | 10%        | Exactly 5 cycles later                     |       |          |

|     | 5%         | Exactly 6 cycles later                     |       |          |

|     | 5%         | Exactly 7 or more cycles later             |       |          |

So this means that 30% of loads are immediately followed by a dependent (i.e. 1 cycle later), 20% of loads have a dependent exactly 2 cycles later, 20% have a dependent 3 cycles later, and so on. These classifications are completely disjoint – the 20% of loads that have a dependent 2 cycles later do NOT

Find the TCPI of this new architecture:

$$4.125$$

$TCPI_{New} = BCPI_{new} + MCPI_{new} = 1.575 + 2.55$

$BCPI_{new} = 1 + 0.25(0.3 \times 3 + 0.2 \times 2 + 0.2 \times 1) + \frac{1}{3} \times 0.15 \times 4 = 1.575$

$lw depend$

$br penalty$

$MCPI_{new} = MCPI_{oid} = 2.55$

Assume your target application will run 1M instructions. Find the execution time of this architecture for that application:

ET:

$$\frac{f_{1}125 \times 10^{-4} \text{ seconds}}{\text{CT} = 100 \text{ pico seconds}} = 100 \times 10^{-12} \text{ seconds}$$

$\frac{\text{Cycles}}{\text{inst}} \times \frac{\text{sec}}{\text{cycle}} \times \frac{\text{Inst}}{\text{cycle}} = \text{sec}$

THE STATE OF STATE OF